AC

STUDENT HANDOUT KDA-5042

E3ABP30534M 000

E3AZP30554 000

## Technical Training

JSS DATA PROCESSOR AND DISPLAY MAINTENANCE

HMP-1116 INTRODUCTION

MAY 1986

## USAF TECHNICAL TRAINING SCHOOL

3300th Technical Training WING

Keesler Air Force Base, Mississippi

---

Designed For ATC Course Use

---

DO NOT USE ON THE JOB

HMP-1116 STUDENT GUIDE

TABLE OF CONTENTS

| CHAPTER     | TITLE                               |

|-------------|-------------------------------------|

| 1           | INTRODUCTION TO THE HMP-1116        |

| 2           | PROGRAMMING MACHINE LANGUAGE        |

| 3           | PROCESSOR BLOCK DIAGRAM DESCRIPTION |

| 4           | MICROINSTRUCTION FORMATS            |

| 5           | READING THE MICROPROGRAM LISTING    |

| 7           | I/O SOFTWARE PROGRAMMING            |

| 8           | INTERRUPTS                          |

| 9           | I/O OPTIONS (PMP, PCC, MPC, RMM)    |

| 10          | MEMORY                              |

| 11          | POWER FAULT DETECT                  |

| APPENDIX 1. | DEFINITIONS OF MNEMONICS            |

| APPENDIX 2. | MICROPROGRAM LISTING DESCRIPTION    |

HMP-1116 Computer

## HMP-1116 COMPUTER

### CHARACTERISTICS

- ARITHMETIC ..... TWO'S COMPLEMENT, INTEGER

- DATA WORD LENGTHS ..... 8, 16, 32, 48, AND 64 BITS

- DATA TYPES ..... FIXED-POINT AND FLOATING-POINT

- DATA FLOW ..... 16-BIT PARALLEL (HALFWORDS)

- ALU WIDTH ..... 32-BIT

- INSTRUCTION WORD LENGTH ..... 16 AND 32 BITS

- GENERAL REGISTERS ..... SIXTEEN 16-BIT HARDWARE REGISTERS AND EIGHT 48-BIT FLOATING -POINT MEMORY REGISTERS

- STORAGE (READ/WRITE) ..... RANDOM ACCESS, DYNAMIC INTEGRATED CIRCUIT, LIMITED NON-VOLATILITY VIA BATTERY BACKUP

- STORAGE SIZE (MAXIMUM)..... 131,072 HALFWORDS (17 BITS EACH INCLUDING ONE PARITY BIT)

## 1.0 INTRODUCTION TO THE HMP-1116

The HMP-1116 minicomputer is a microprogrammable, general purpose, digital computer providing high-speed computation and data processing. The computer provides hardware capabilities for operating on binary data in field lengths of 8-bit bytes, 16-bit halfwords, and optional 32-bit full words, and 48-bit floating-point words. The computer is organized into functional units to achieve modularity at the card level for adding optional capabilities. The modularity allows various functional configurations without affecting existing card designs. The degree of flexibility includes variable memory size (128K halfwords maximum), ability to add, delete, and modify user instructions, Real Time Counter and Elapsed Time Counter option, extension to a 32-bit arithmetic logic unit (ALU), and Cordic shift network option (Trigonometric function).

The purpose of the HMP-1116 is to provide the capability to execute a program consisting of a sequence of software instructions and to communicate with external devices (peripherals). A software instruction is a binary word with a predefined format that the computer will recognize and execute. A program consists of a group of software instructions. The instructions in a program are located in consecutive memory locations.

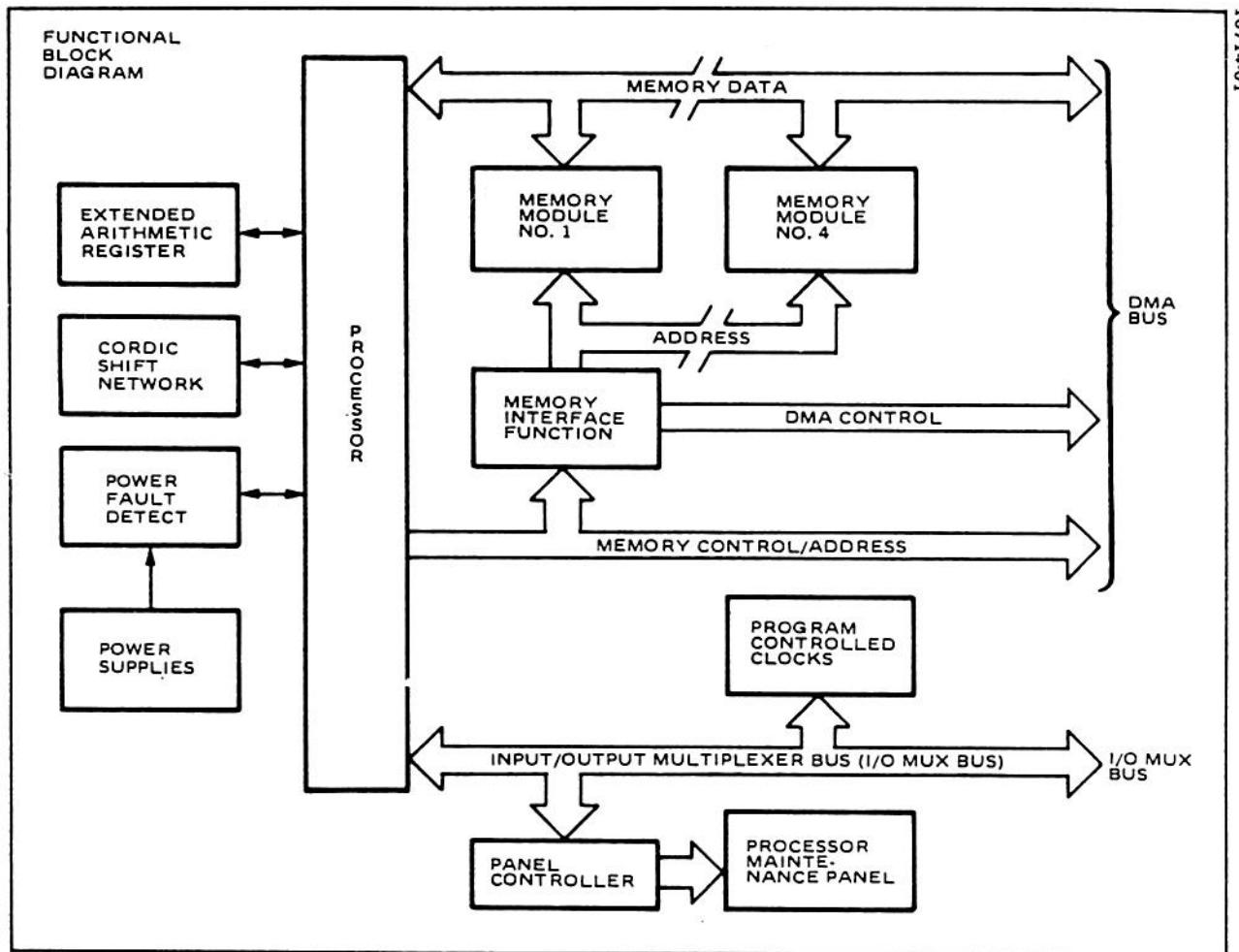

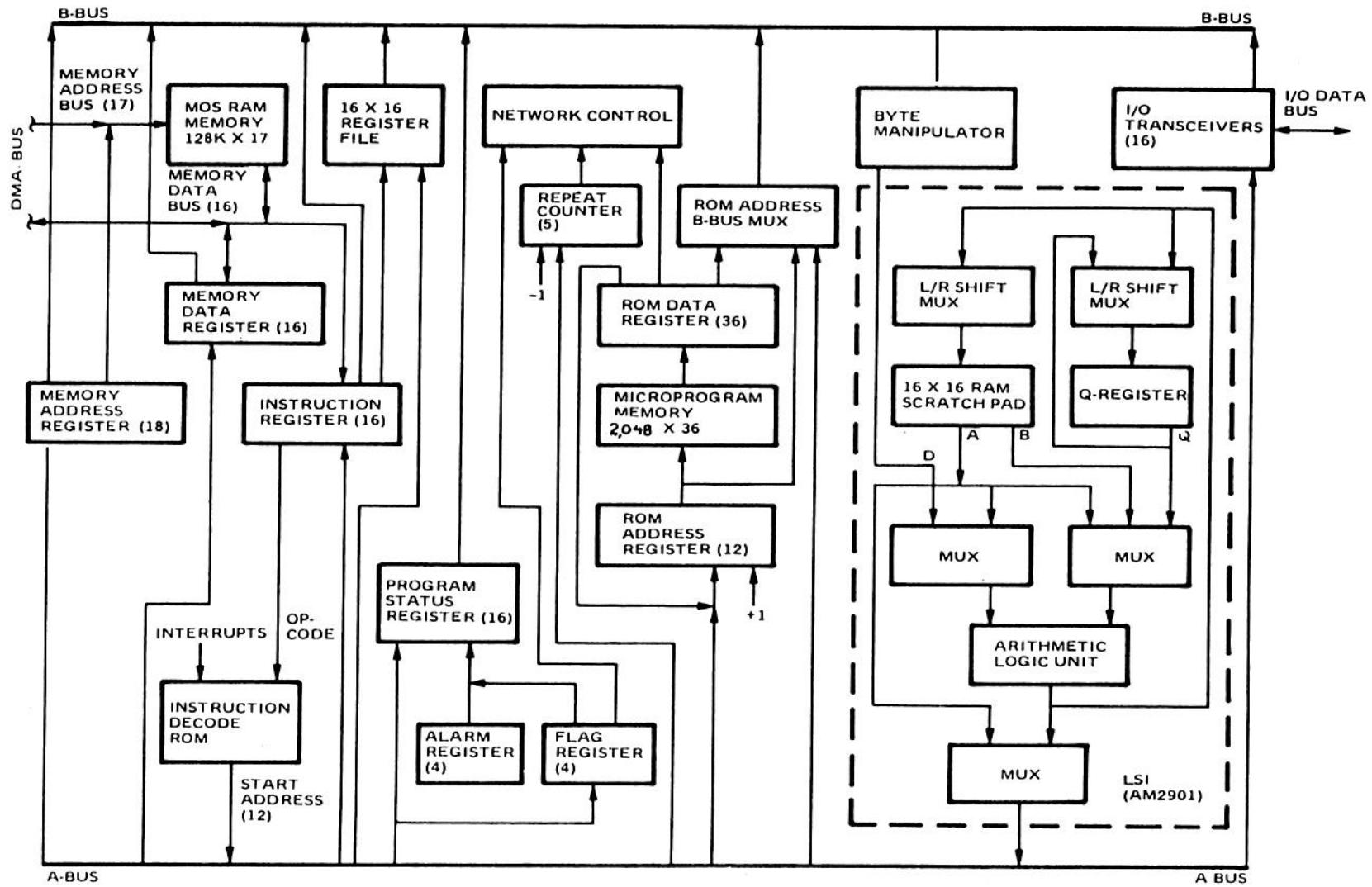

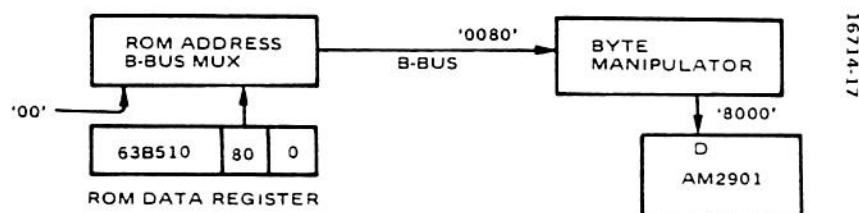

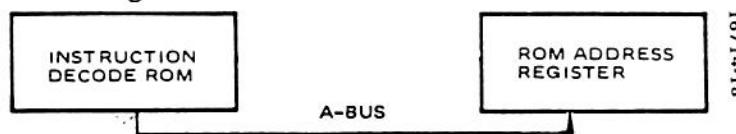

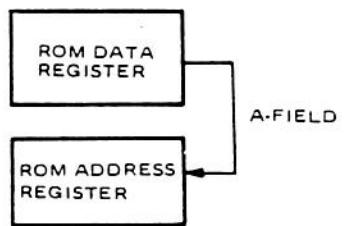

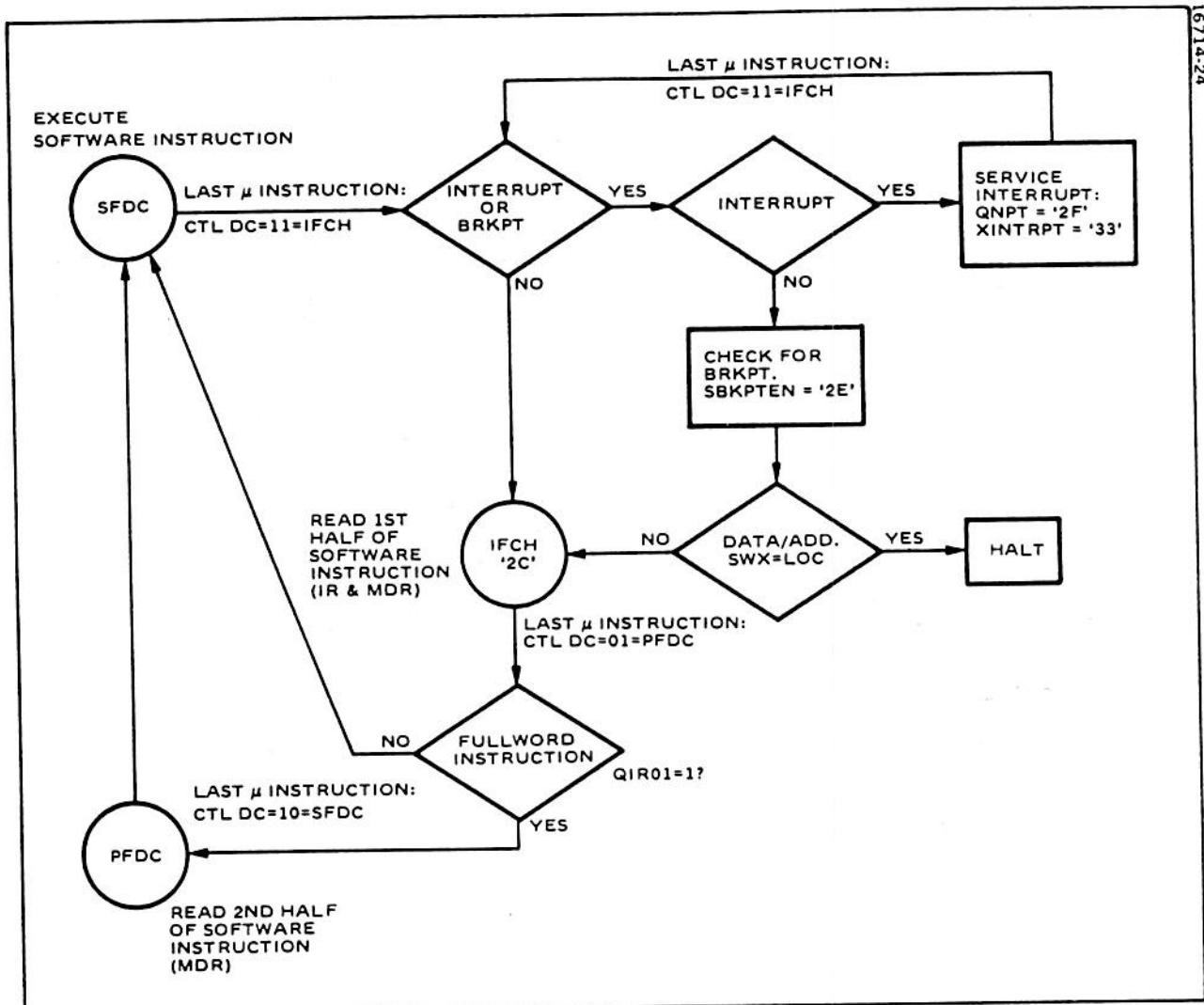

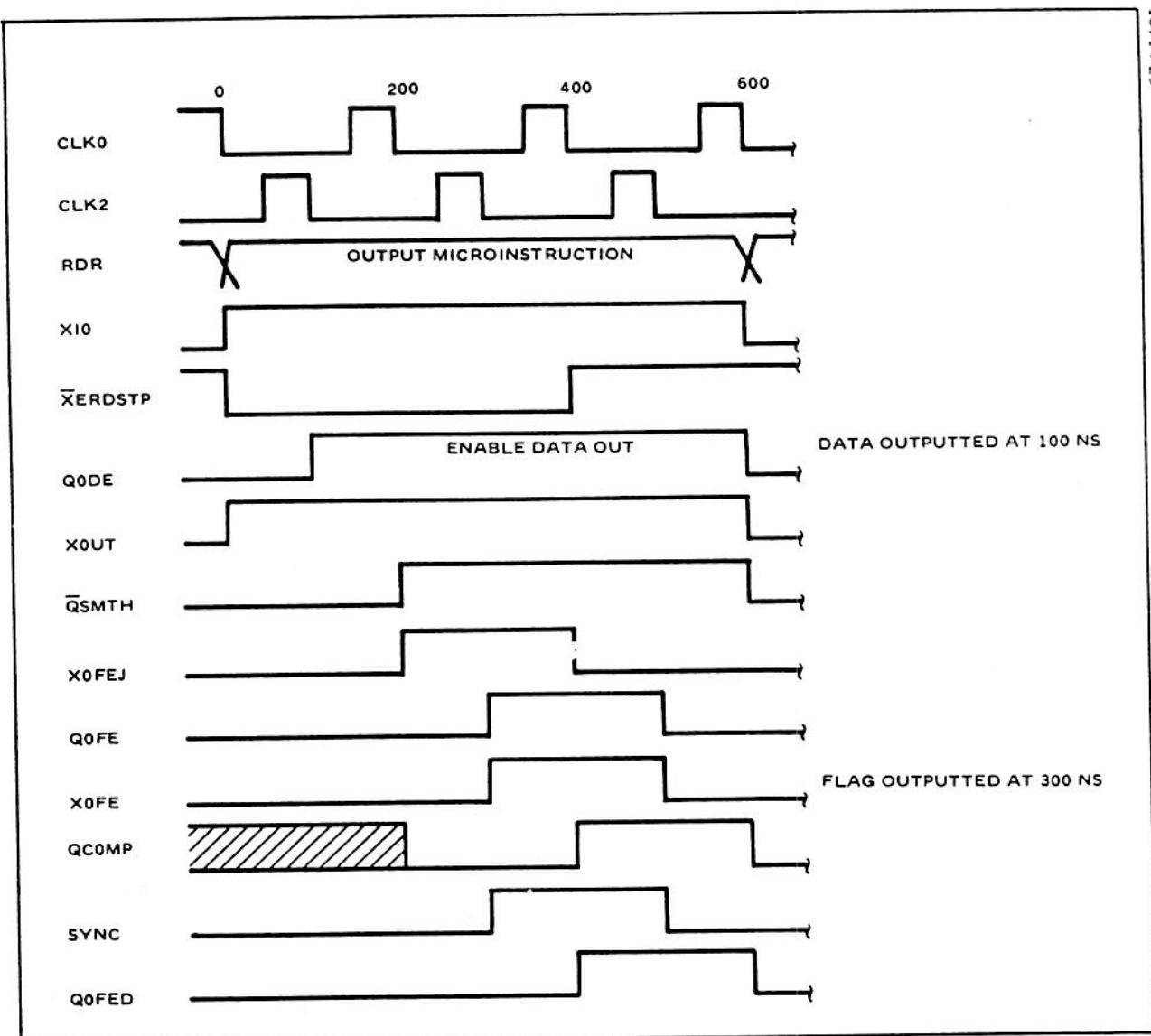

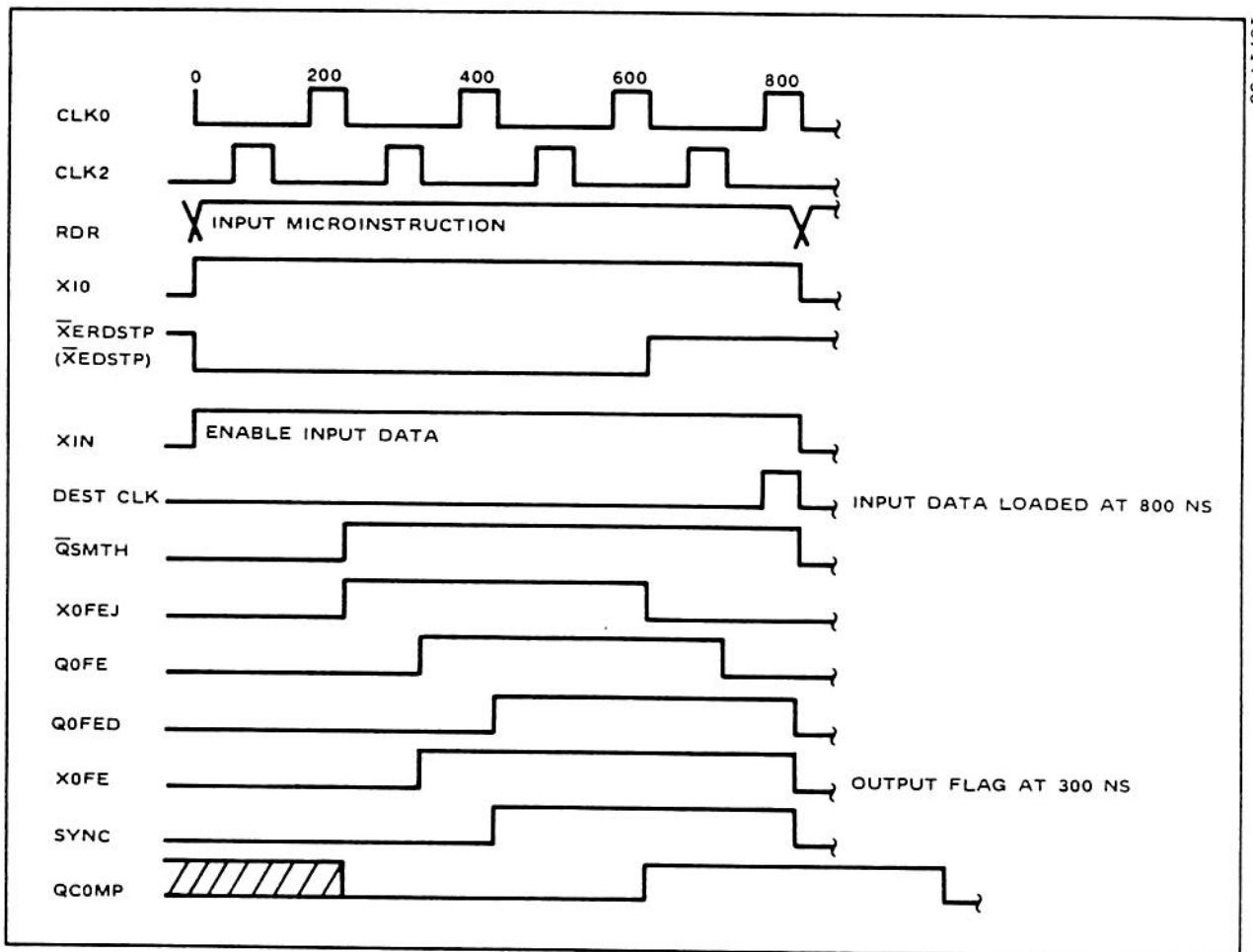

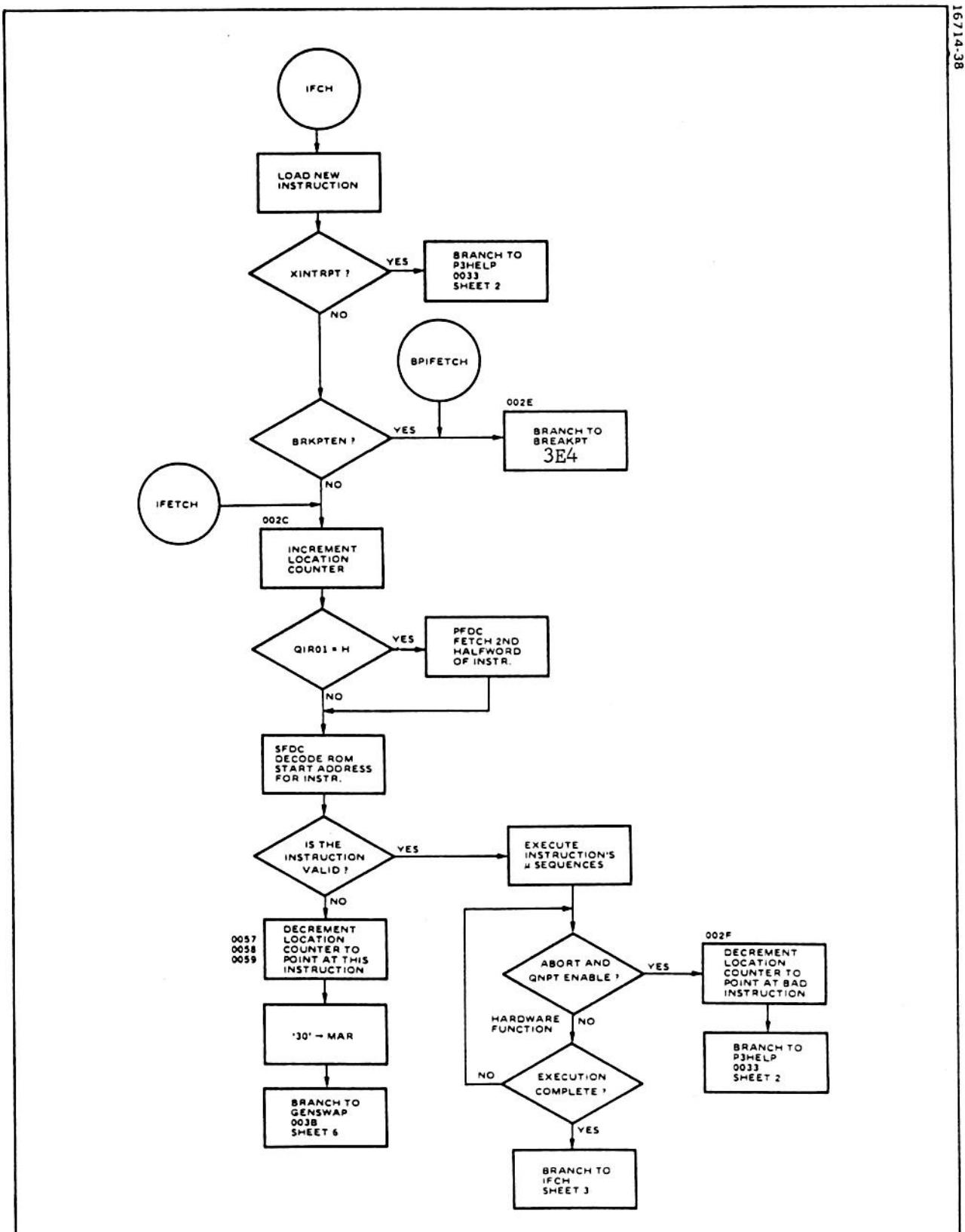

**1.1 Microsequencer.** Figure 1-1 is a basic architecture of the HMP-1116 minicomputer. The central controlling function is the microsequencer function. This function consists of the Rom Address Register, Microprogram Memory and Rom Data Register. The Microprogram Memory is a read only memory (ROM) and contains up to 2,048 36-bit microinstructions. The Microprogram Memory is addressed by the Rom Address Register (RAR). The 36-bit microinstruction read from the Microprogram Memory is loaded into the Rom Data Register (RDR). Each microinstruction is broken into fields which are used to control the RAR, arithmetic operations, hex digit (4-bit) and byte (8-bit) manipulations, data movement between registers, input/output operations, memory and software execution. The Network Control is responsible for decoding the microinstruction in order to control these functions.

The microinstructions are arranged in sets within the Microprogram Memory. A set of microinstructions is called a microsequence. Each microsequence is responsible for performing a specific task.

While performing a specific microsequence, the RAR will count up by 1 every 200ns. To locate the next microsequence the RAR must be loaded with a new value. The RAR will be loaded 1) for a microprogram branch, 2) when a software instruction is to be executed or 3) on an interrupt.

The microprogram branch is implemented by taking a 12-bit field from the RDR and loading the RAR.

There is a microsequence in the Microprogram Memory for each software instruction. The start addresses for these microsequences are provided by the Instruction Decode Rom.

The Instruction Decode Rom also provides the start address for the interrupt service microsequence. Interrupts are generated from functions external to the microprocessor. The following analogy may promote further understanding:

Let's say you are reading this document and your phone rings. This is an interrupt. When you answer the phone you have acknowledged the interrupt. Your conversation is service for the interrupt. Following your conversation you return to reading this document. The processor performs the same steps when receiving an interrupt. First it acknowledges the interrupt, then it performs the necessary service. Following this service the processor returns to its previous duties.

If the execution of a microinstruction takes more than 200ns (1 clock cycle), the RAR and RDR will be held until the operation is complete. Three cases in which this hold will occur are memory operations, input/output (I/O) operations and repeat operations.

Repeat operations are controlled by the Repeat Counter. This counter will allow a single microinstruction in the RDR to be repeated a maximum of 31 times.

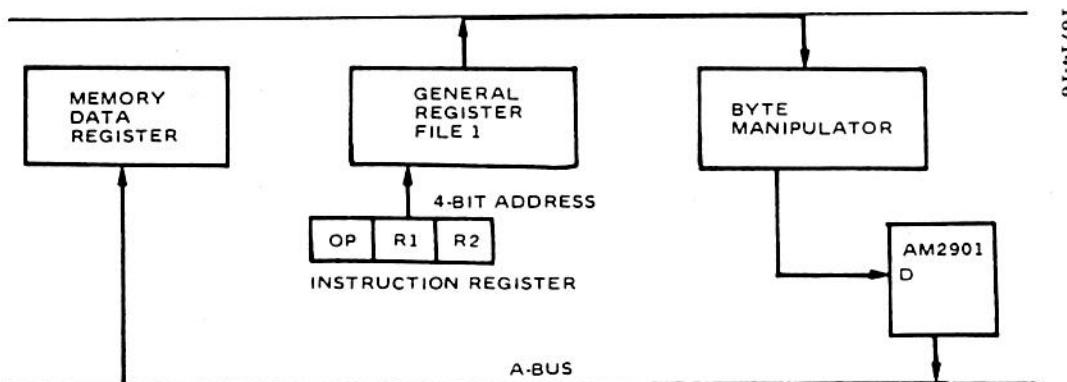

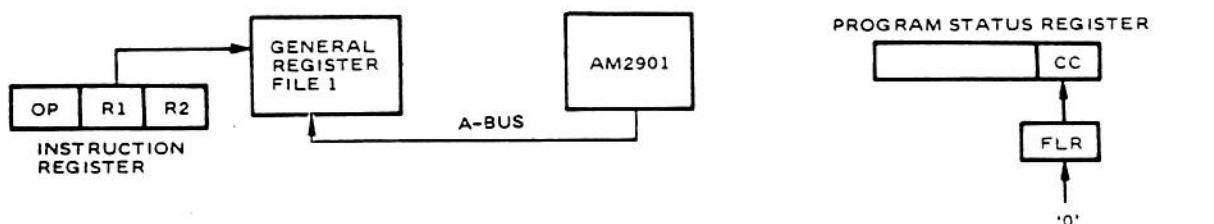

1.2 Arithmetic Logic Unit (ALU). The ALU is a 16-bit arithmetic function which can be expanded to a 32-bit arithmetic function. The ALU is under direct control of the microprogram and is responsible for performing all logical and arithmetic operations. The ALU function consists of the Byte Manipulator, Flag Register and AM2901 large scale integrated circuits (LSI). Each AM2901 chip provides 4 bits of ALU. Therefore, a 16-bit ALU requires four AM2901s.

The AM2901s will either perform an arithmetic or logical function, or pass data unchanged to the A-bus output. The specific operation is dictated by the microprogram. The AM2901s also provide 16 scratch pad registers (internal registers) which are used by the microprogram as a work area. There is also a Q register which is used during multiply, divide and shift operations.

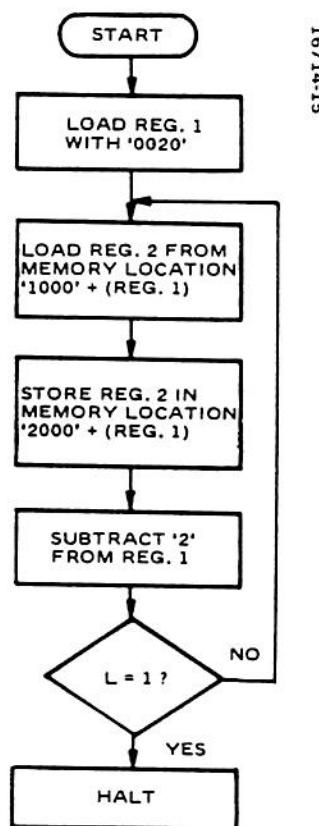

The Flag Register (FLR) is a four bit register used to indicate the magnitude of the arithmetic result. The four bits of the FLR are called the C, V, G and L flags.

The C (carry) flag is set when a carry out is generated from the AM2901.

The V (overflow) flag is set when an arithmetic overflow occurs. An example of an overflow is when two numbers with like signs are added and produce a result with a different sign.

The G (greater than) flag is set when the arithmetic result is greater than zero.

The L (less than) flag is set when the arithmetic result is less than zero.

The FLR may be examined by the microprogram in order to make decisions based on a previous operation.

The Byte Manipulator is under microprogram control. This function allows the following operations to be performed:

- 1) byte exchange

- 2) hex digit extraction

- 3) no change to data

A byte exchange operation means that the 8 MSBs and 8 LSBs of a 16-bit value on the B-bus are exchanged. The new 16-bit word is then applied to the direct input of the AM2901.

#### Example of Byte Exchange:

Input from the B-bus(In hex) = 'ABCD'

Output of the Byte Manipulator = 'CDAB'

Hex digit extraction allows any one of the 4 hex digits of a 16-bit word to be placed in the hex LSD position. The three hex MSDs are set to zero.

#### Example of Hex Digit Extraction:

Input to the Byte Manipulator(In hex) = 'ABCD'

Output of the Byte Manipulator for extracting MSD = 'OOOA'

Byte Manipulator Output for extracting second MSD = 'OOOB'

Byte Manipulator Output for extracting third MSD = 'OOOC'

Byte Manipulator Output for extracting the LSD = 'OOOD'

1.3 Data Movement Between Registers. Data can be transferred from an internal or external register to an internal or external register. The register sending data is called the source. The register receiving data is called the destination. The source and destination registers are specified by the microprogram.

Data is 16 bits of arithmetic or logical information. A 16-bit arithmetic value consists of data (15 LSBs) and a sign bit (MSB). Negative values are in two's complement and have a sign bit set high. Logical values consist of 16 bits of unsigned data.

A source register can be an internal register, the Q register, an external register or data from an I/O device (via the I/O transceivers). External registers include all registers outside the dotted lines on Figure 1-1. A list of external registers which can be specified by the microprogram as a source is shown below.

- 1) Rom Data Register (RDR)

- 2) Rom Address Register (RAR)

- 3) Program Status Register (PSR)

- 4) Any one of the 16x16 Register File

- 5) Instruction Register (IR)

- 6) Memory Address Register (MAR)

- 7) Memory Data Register (MDR)

A destination register can be an internal register, the Q register, an external register or data to an I/O device (via the I/O transceivers). A list of external registers which can be specified by the microprogram as a destination is shown below.

- 1) Rom Address Register

- 2) Repeat Counter (CTR)

- 3) Flag register (FLR)

- 4) Program Status Register

- 5) Any one of the 16x16 Register File

- 6) Instruction Register

- 7) Memory Data Register

- 8) Memory Address Register

An external source register is placed on the B-bus and passes through the Byte Manipulator to the AM2901. An external destination is loaded from data placed on the A-bus by the AM2901.

If data is moved from one internal register to another, the source register contents can be passed onto the A-bus, through the Rom Address B-Bus Mux, to the B-bus, through the Byte Manipulator to the D input of the AM2901 and loaded into the destination register. This operation will be performed when an internal register is to be modified by the Byte Manipulator.

The Rom Address B-Bus Mux is also used when the RDR or RAR is specified as the source. The RAR will be specified as a source if it needs to be saved in an internal register. The RDR is specified as the source if a field of data from the microinstruction is to be loaded into an internal register.

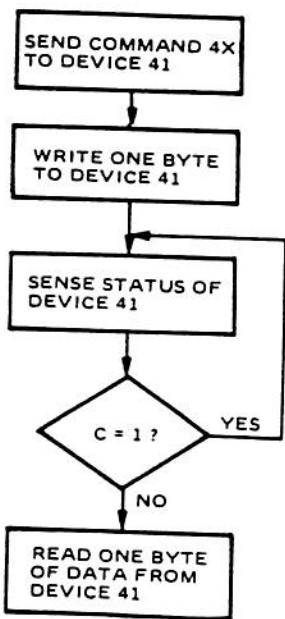

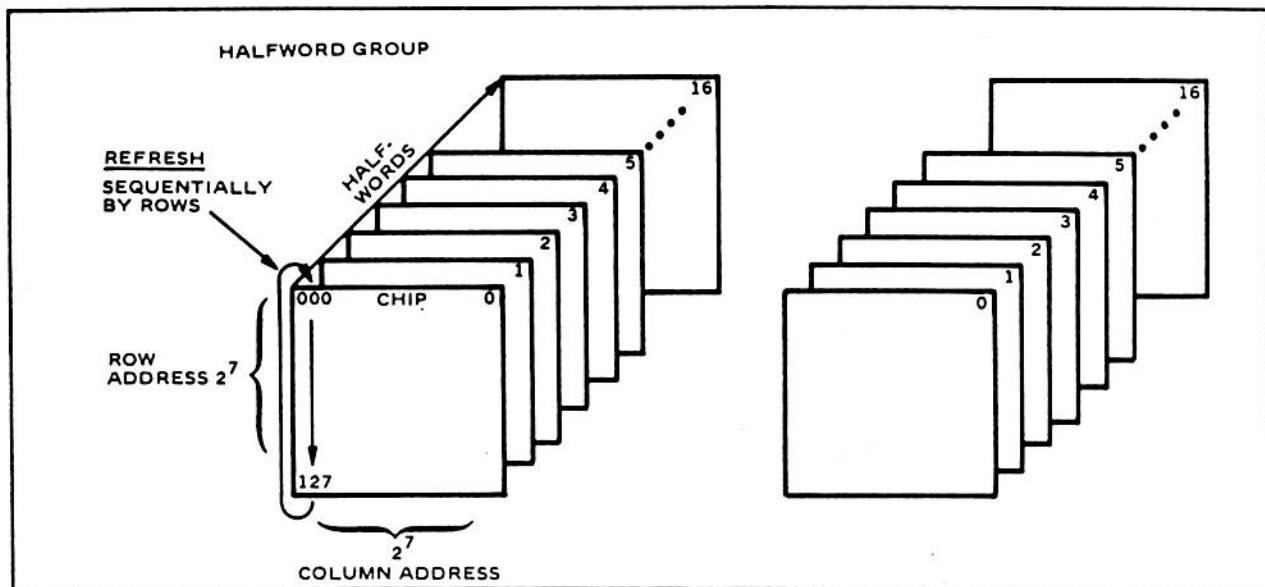

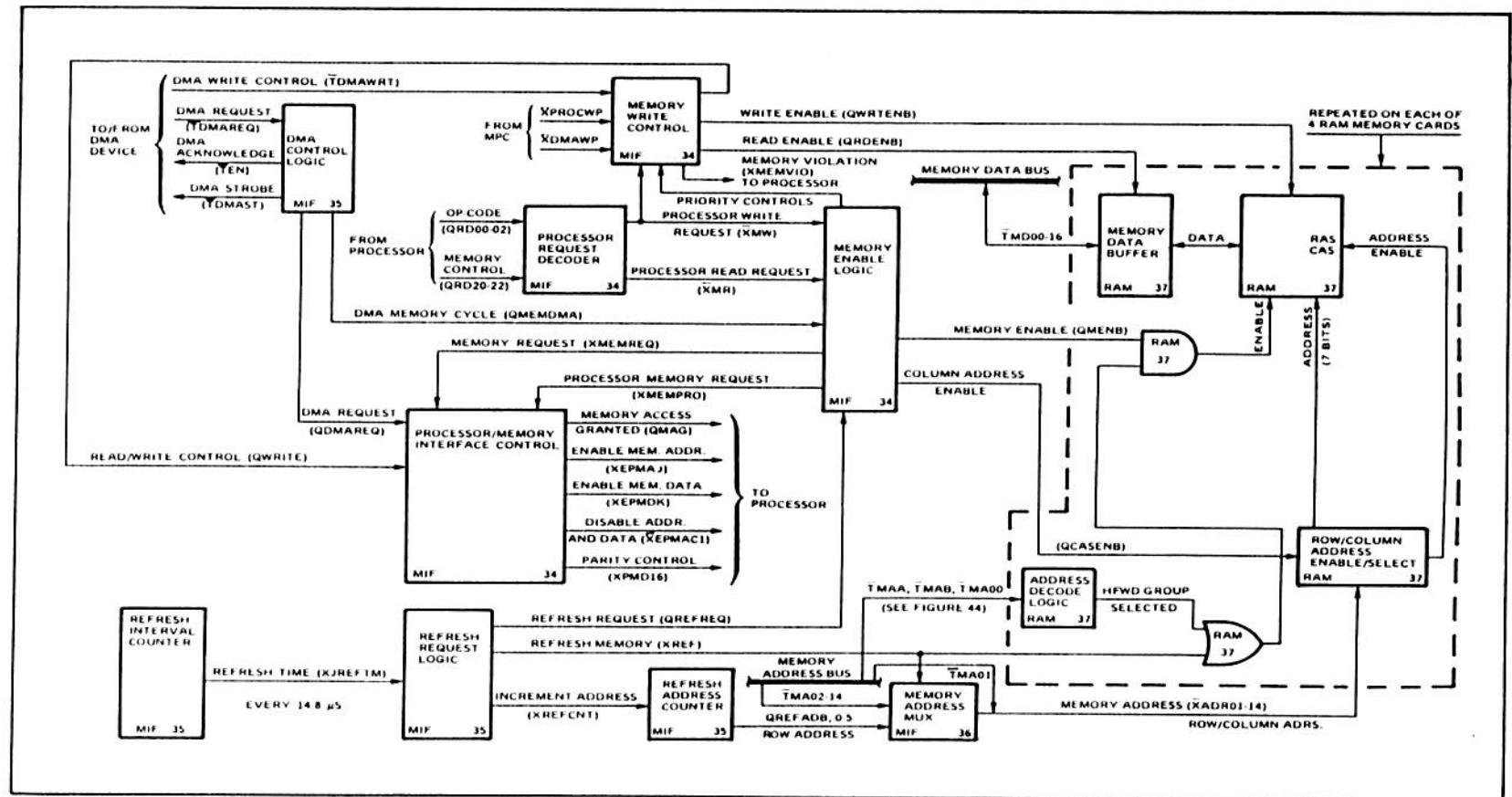

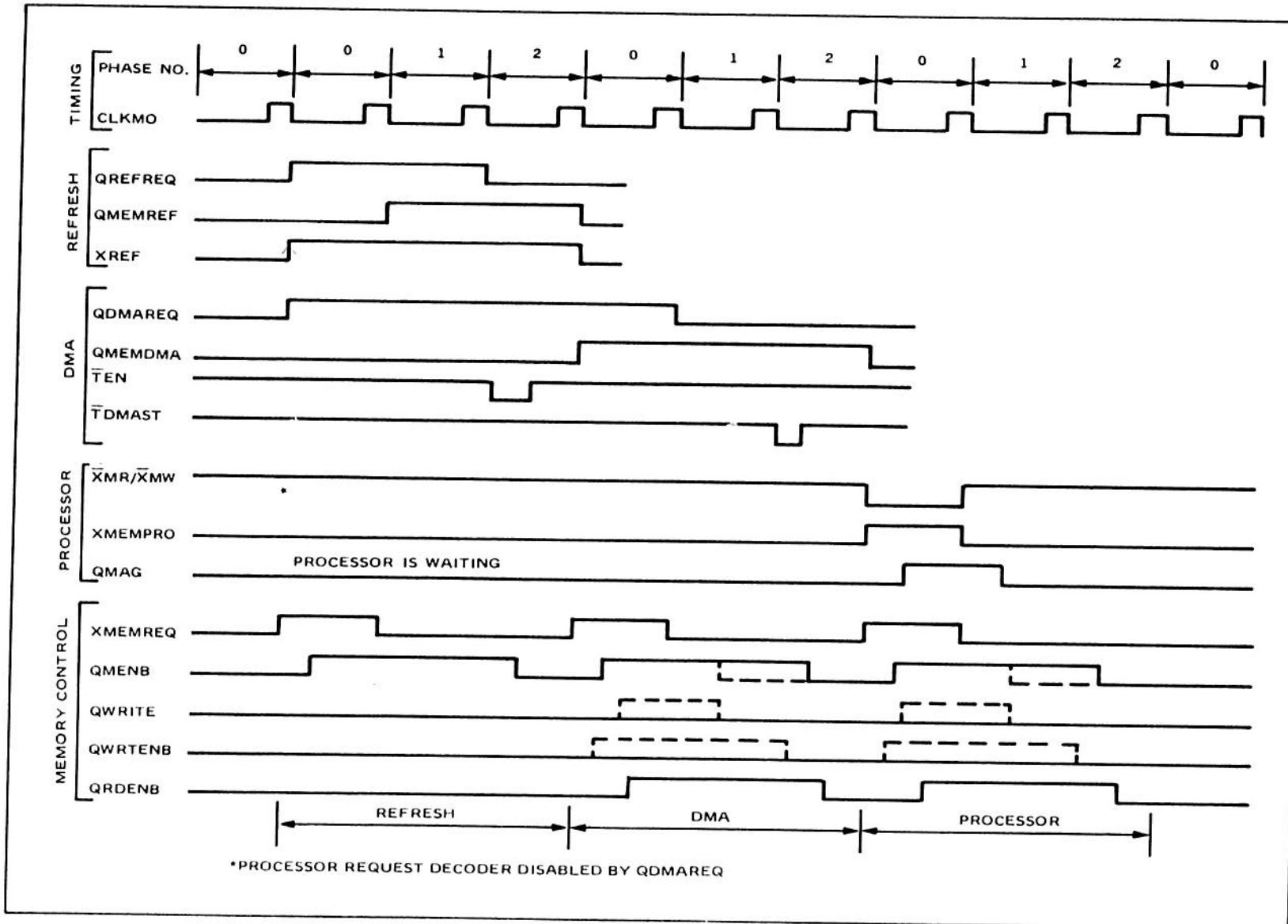

**1.4 MOS RAM Memory.** The MOS RAM Memory is used by the programmer to store his program and data. The memory in the HMP-1116 can be varied in size by addition or deletion of memory cards (32K each). The maximum memory configuration is 131,072 (128K, where 1K = 1,024) 16-bit words. For each location in memory there are 17 bits (16 data bits plus 1 parity bit). When a word is stored in memory, a parity bit is also stored to provide odd

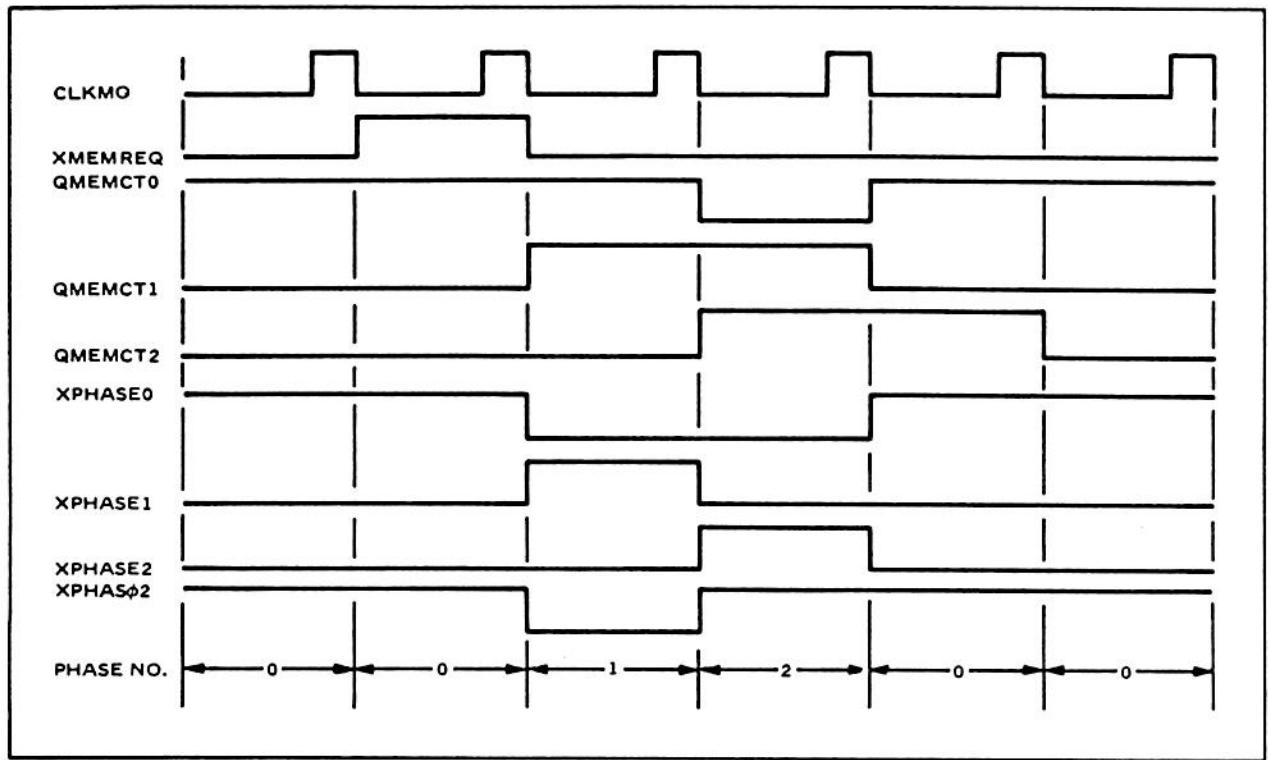

parity (odd number of 1s). When data is read from memory this parity is checked. A memory cycle (time required to read or store data) is 600ns. Since the RAM Memory is MOS type it requires a refresh cycle every 14.8 microseconds.

There are three functions that access memory. These are listed below from highest priority to lowest.

- 1) Refresh

- 2) DMA (Direct Memory Access)

- 3) Processor

### Processor Memory Requests

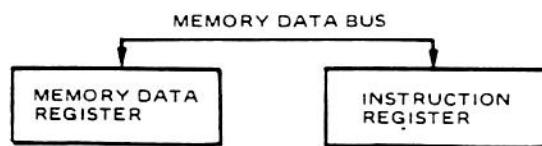

The processor uses four registers for memory operations. These are the Memory Address Register (MAR), Memory Data Register (MDR), Instruction Register (IR), and Program Status Register (PSR).

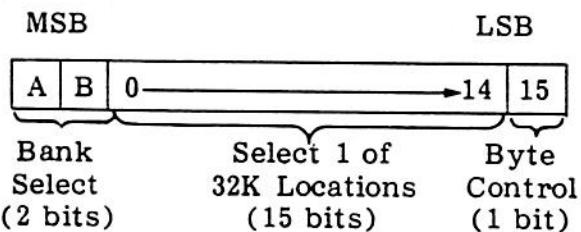

The Memory Address Bus is used to locate one of 128K words in memory. The two MSBs (PSR8:9 during Instruction Fetch or PSR10:11 during Operand Read) select one of four memory banks (32K each). The LSB of the MAR is not sent to the bus, instead it is provided to the Byte Manipulator for control byte operations. The remaining 15 bits of the MAR are used to select one of 32K words within a memory bank.

A byte operation is when an 8-bit byte is extracted from a 16-bit source register, or when an 8-bit byte is inserted into 8 bits of a 16-bit destination register.

In an extract operation the MDR is the source. Either the 8 MSBs or the 8 LSBs can be selected as the byte operand. If the LSB of the MAR is 0, the Byte Manipulator selects the 8 MSBs. If the LSB of the MAR is 1, the Byte Manipulator selects the 8 LSBs.

### Byte Extraction Example

| <u>MAR LSB</u> | <u>Byte Manipulator Input</u> | <u>Byte Manipulator Output</u> |

|----------------|-------------------------------|--------------------------------|

| 0              | 'ABCD'                        | 'OOAB'                         |

| 1              | 'ABCD'                        | 'OOCD'                         |

In an insert operation an internal register or the MDR is the destination. An 8-bit byte on the 8 LSBs of the B-bus is inserted into either the 8 MSBs or the 8 LSBs of the destination register, leaving 8 bits of the destination unchanged. If the LSB of the MAR is 0, a byte is inserted into the 8 MSBs of the destination. If the LSB of the MAR is 1, a byte is inserted into the 8 LSBs of the destination.

Byte Insertion Example:

| <u>Destination Before</u> | <u>Byte Manipulator Input from B-bus</u> | <u>MAR LSB</u> | <u>Destination After</u> |

|---------------------------|------------------------------------------|----------------|--------------------------|

| '1234'                    | 'OOAB'                                   | 0              | 'AB 34'                  |

| '1234'                    | 'OOAB'                                   | 1              | '12AB'                   |

The MDR is used to hold data read from memory or data to be written into memory.

The IR is loaded with a software instruction read from memory. This instruction is broken into fields. One of these fields, called the op-code, defines the type of instruction and the operation to be performed. The op-code is decoded by the Instruction Decode Rom to provide a microsequence start address, which is loaded into the RAR. At this point the software instruction will be executed by its unique microsequence residing in the Microprogram Rom. Another field from the software instruction allows the programmer access to the 16x16 Register File. These registers are usually called General Registers. When the microprogram uses the 16x16 Register File as a source or destination, the software instruction in the IR specifies which one of the 16 registers is to be used.

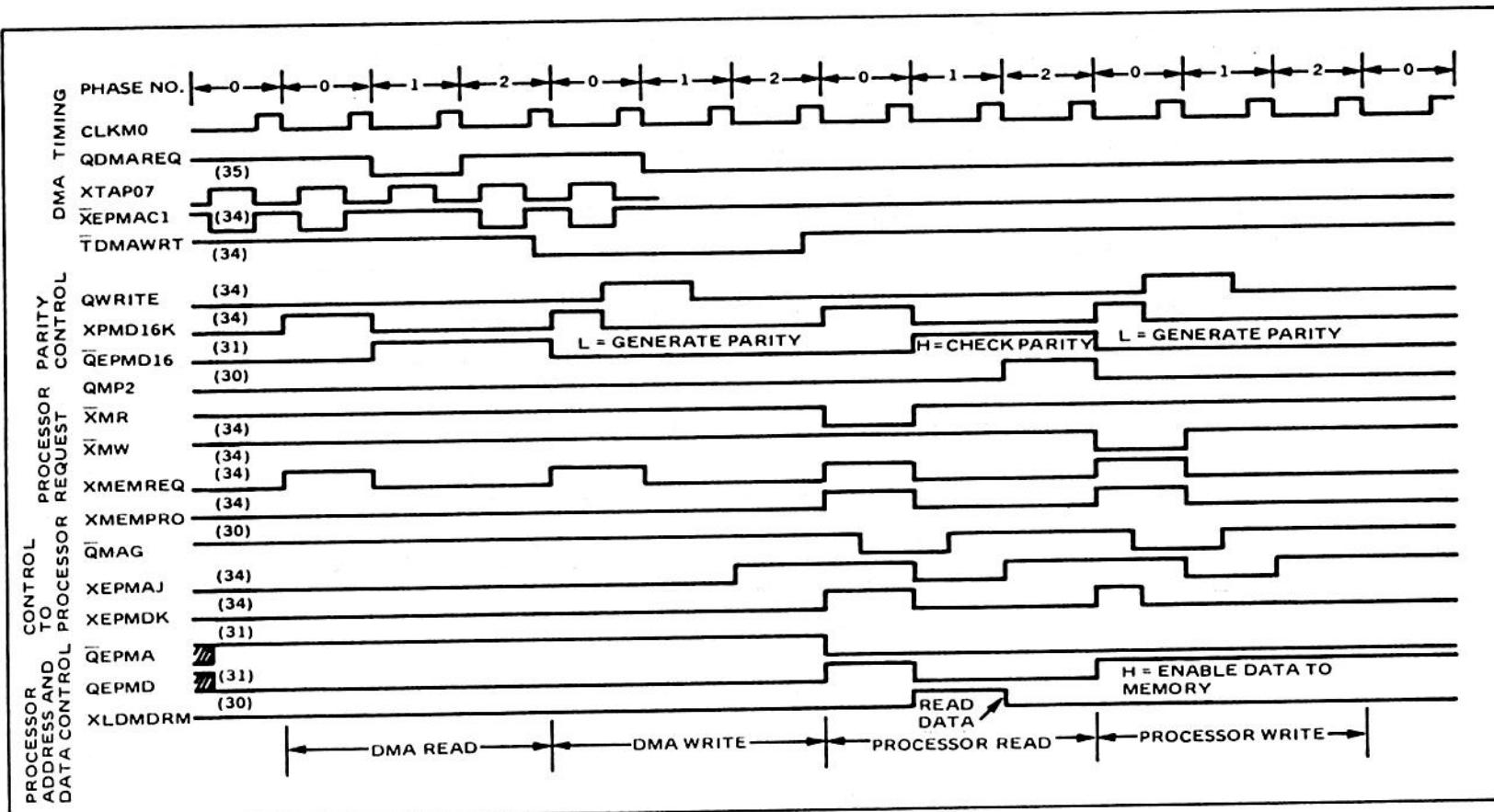

DMA Memory Requests

The Direct Memory Access (DMA) port allows an external device to address the memory and either read or write data. The DMA interface will be discussed in detail later in this chapter.

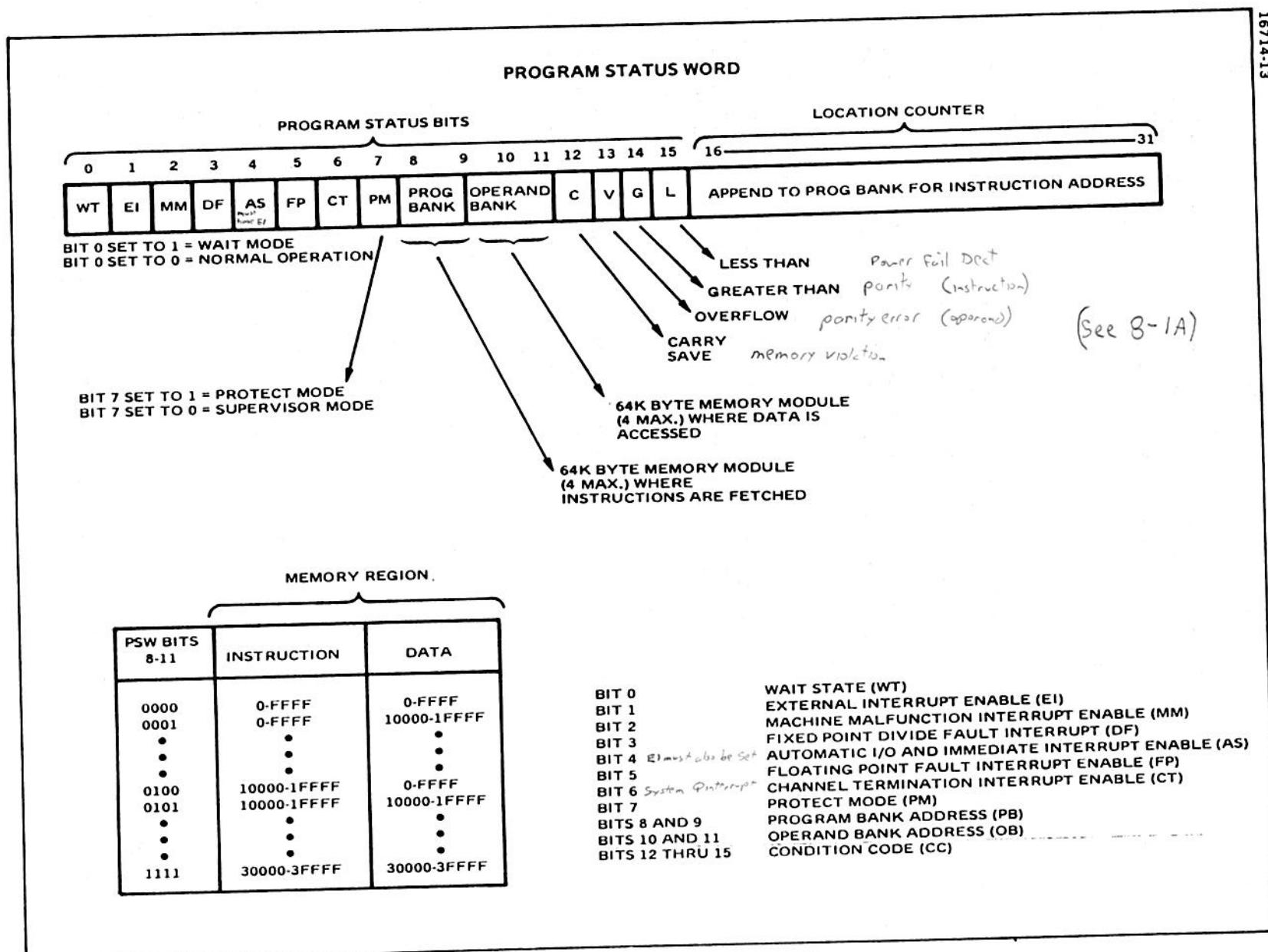

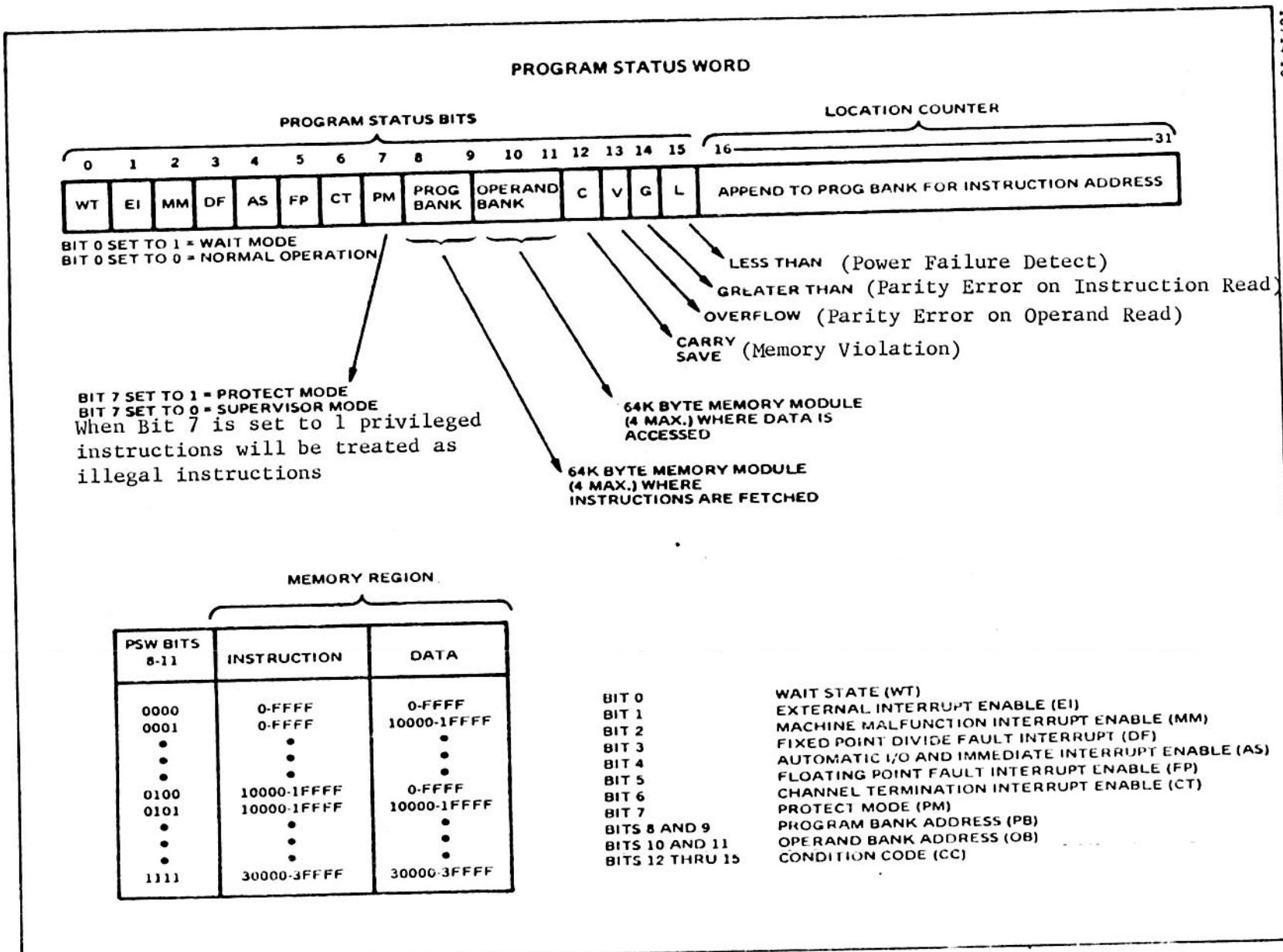

**1.5 Program Status Word.** The Program Status Word (PSW) consists of a 16-bit external register called the Program Status Register (PSR) and a 16-bit internal register which is called the Location Counter.

The Location Counter (LOC) is used by the microprogram to locate the next software instruction in memory to be executed. Each time an instruction is read from memory and loaded into the Instruction Register, the LOC is incremented to point to the next instruction.

The PSR contains information that the programmer can use to control software branching and to designate the proper memory banks in which his program and data are located. The programmer can change the PSR by using specific software instructions.

| 0    | 1      | 7            | 8            | 9              | 10                                          | 11 | 12 | 15 | 16 | 31 | PSW See (2-2) |

|------|--------|--------------|--------------|----------------|---------------------------------------------|----|----|----|----|----|---------------|

| Wait | Status | Program Bank | Operand Bank | Condition Code | Location Counter<br>$I + R_7 \text{ (ALU)}$ |    |    |    |    |    |               |

The PSR bit 0 (MSB) is called the Wait bit. When this bit is set, program execution halts.

PSR bits 1 through 7 (Status) control interrupt service.

Bits 8 and 9 of the PSR are the Program Bank address. They are used to select one of four banks when reading an instruction from memory.

PSR bits 10 and 11 are the Operand Bank address. They are used to select one of four banks when reading an operand from memory. The Program Bank address or Operand Bank address is loaded into the two MSBs of the MAR by the microprogram to provide the appropriate bank selection.

Bits 12 through 15 of the PSR are the Condition Code. This field is loaded from the Alarm Register (4 bits) or the Flag Register (4 bits).

PSW bits 16 through 31 are the Location Counter (LOC). The LOC is stored in the 16x16 Ram Scratchpad in the AM2901. The LOC defines the memory address of the next software instruction to be executed.

#### Alarm Register

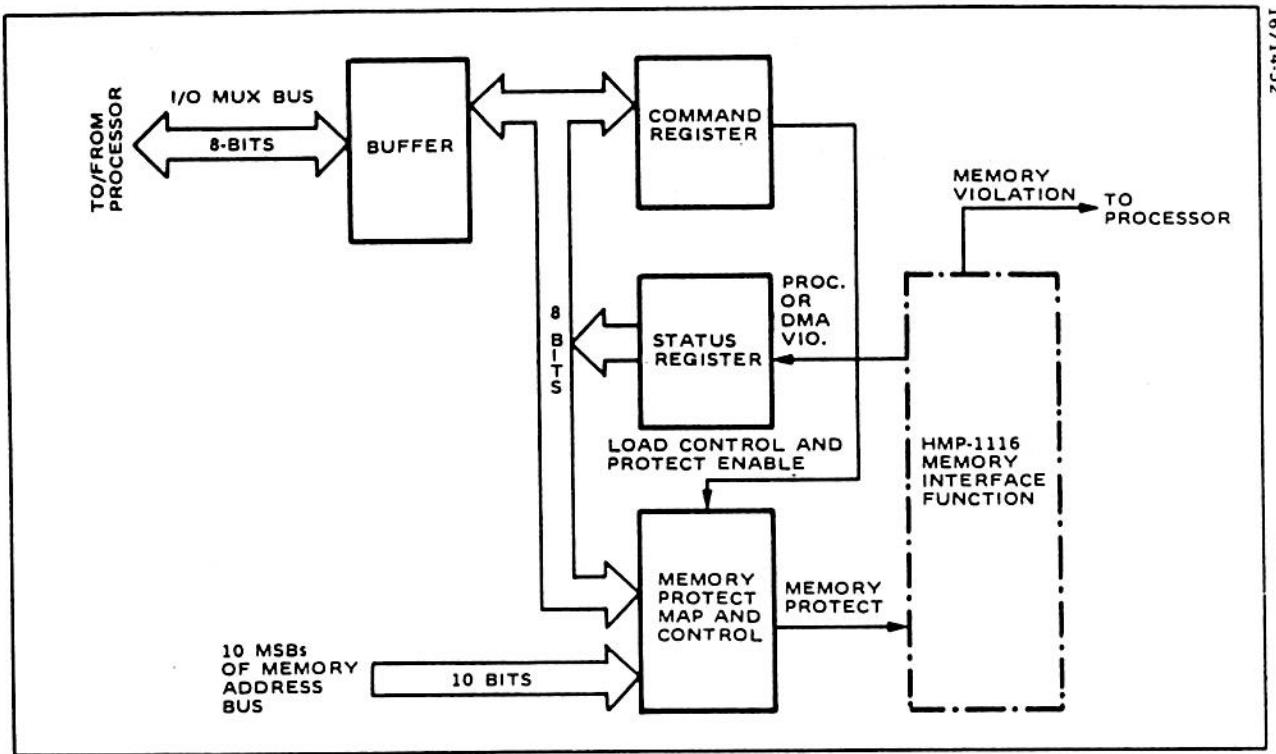

Each bit of the Alarm Register represents a specific hardware fault. The four faults that cause a respective bit in the Alarm Register to be set are memory violation (bit 12), parity error when reading an operand (bit 13), parity error when reading an instruction (bit 14) and power failure (bit 15).

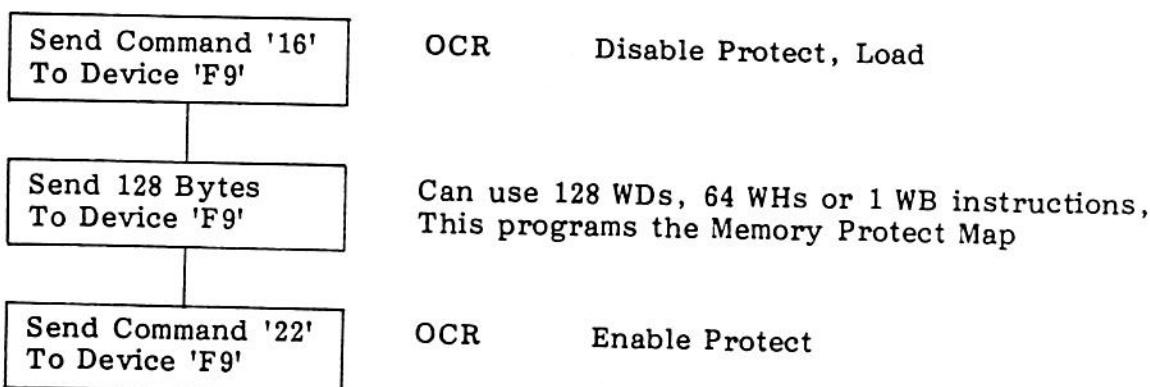

A memory violation can occur only if the computer is equipped with the Memory Protect Controller (MPC) option. The MPC option allows the programmer to designate portions of memory as protected. The software program and DMA will be unable to write into protected memory.

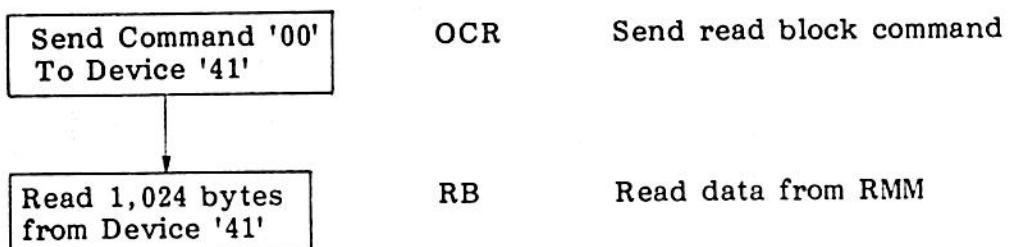

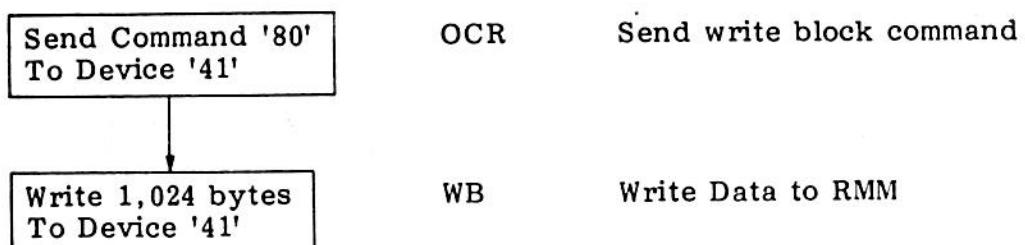

**1.6 Input/Output Operations.** The I/O Mux Bus allows the HMP-1116 to communicate with external devices (peripherals) such as magnetic tape units, card readers or line printers. The interface between the HMP-1116 and the peripheral is indirectly controlled by I/O software instructions. The direct control is provided by the microprogram.

By using appropriate software instructions the programmer can send commands, send or retrieve data and get status information from an I/O

device over the I/O Mux Bus. The software instructions specify General Registers and memory locations that are to be used for I/O transfers. The microprogram uses this information and sequentially controls I/O operations.

The HMP-1116 can communicate with one I/O device at a time. Each device is assigned a unique 8-bit device address. In order to begin communication, the I/O device must first be addressed by the HMP-1116.

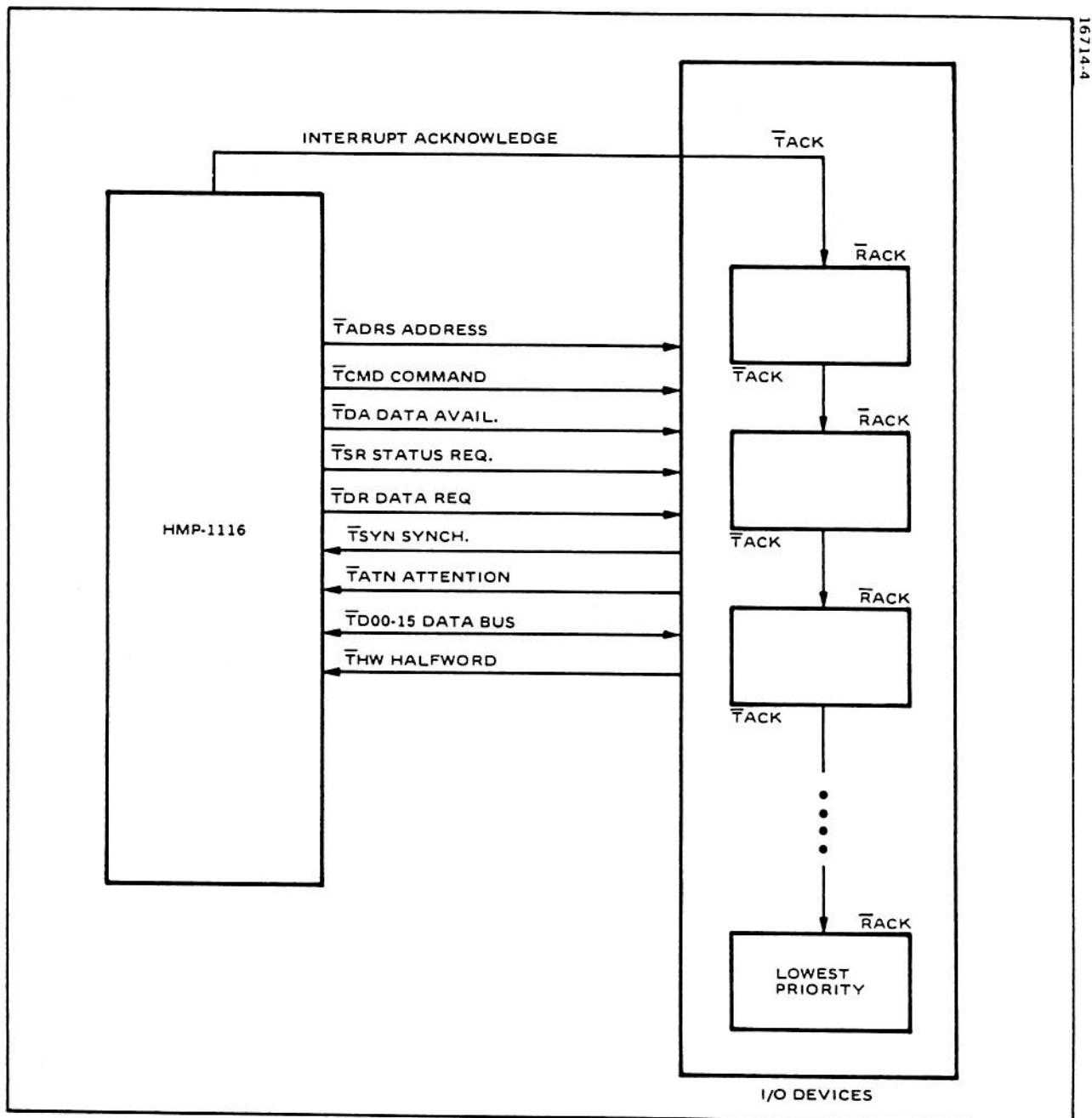

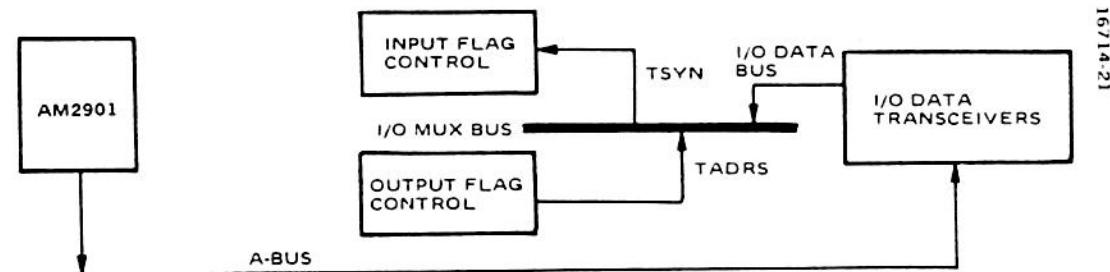

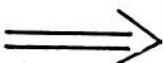

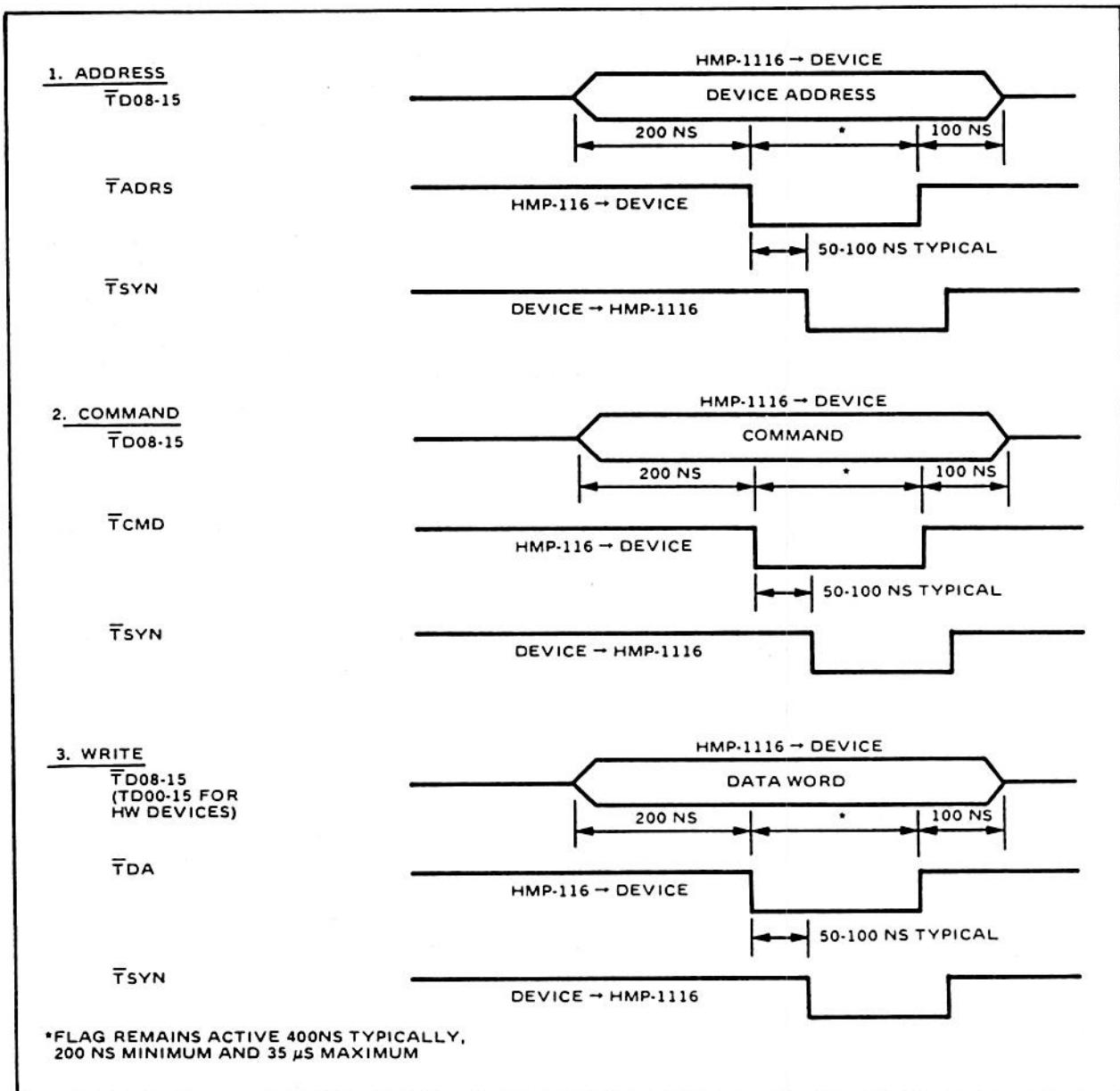

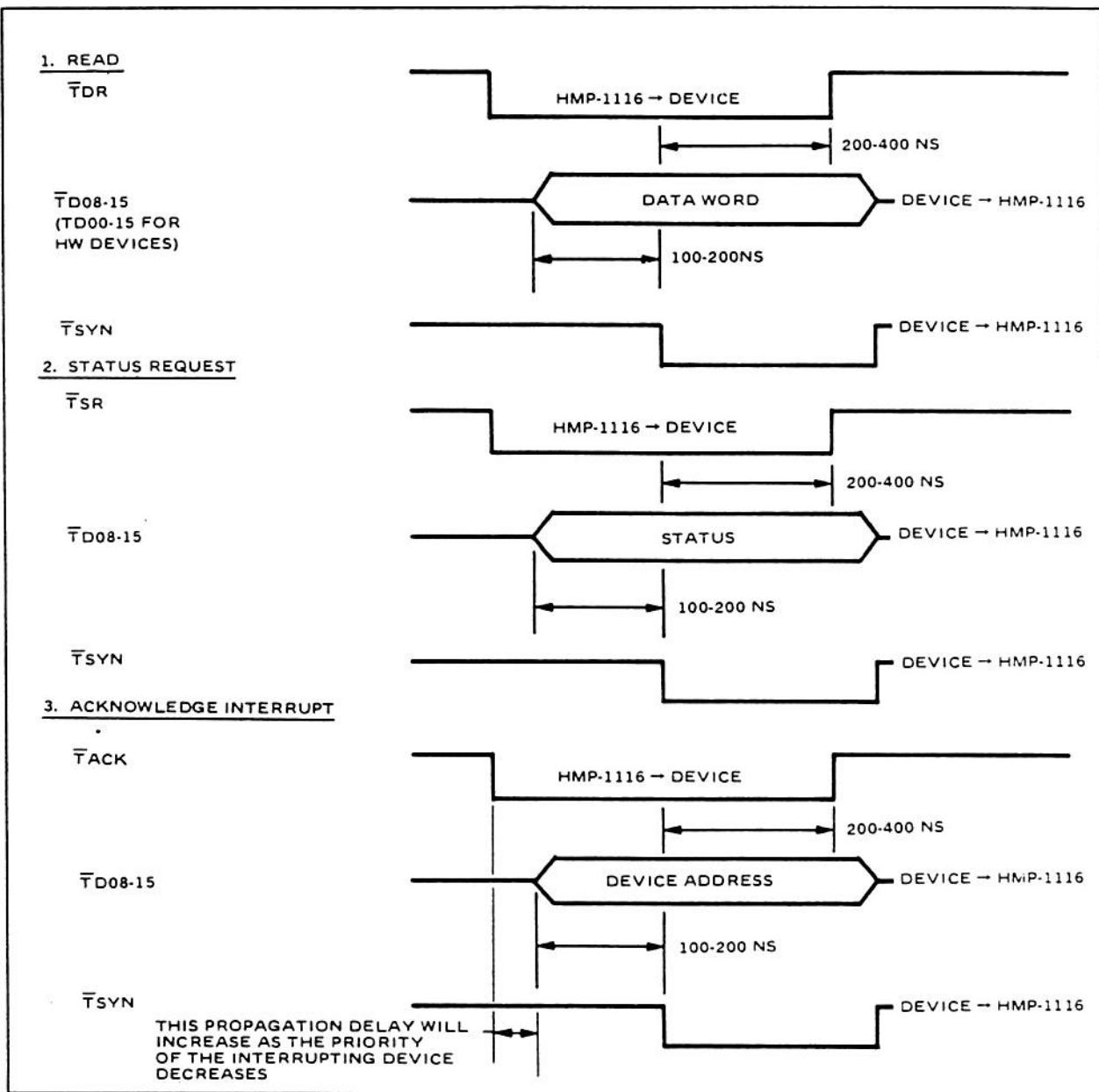

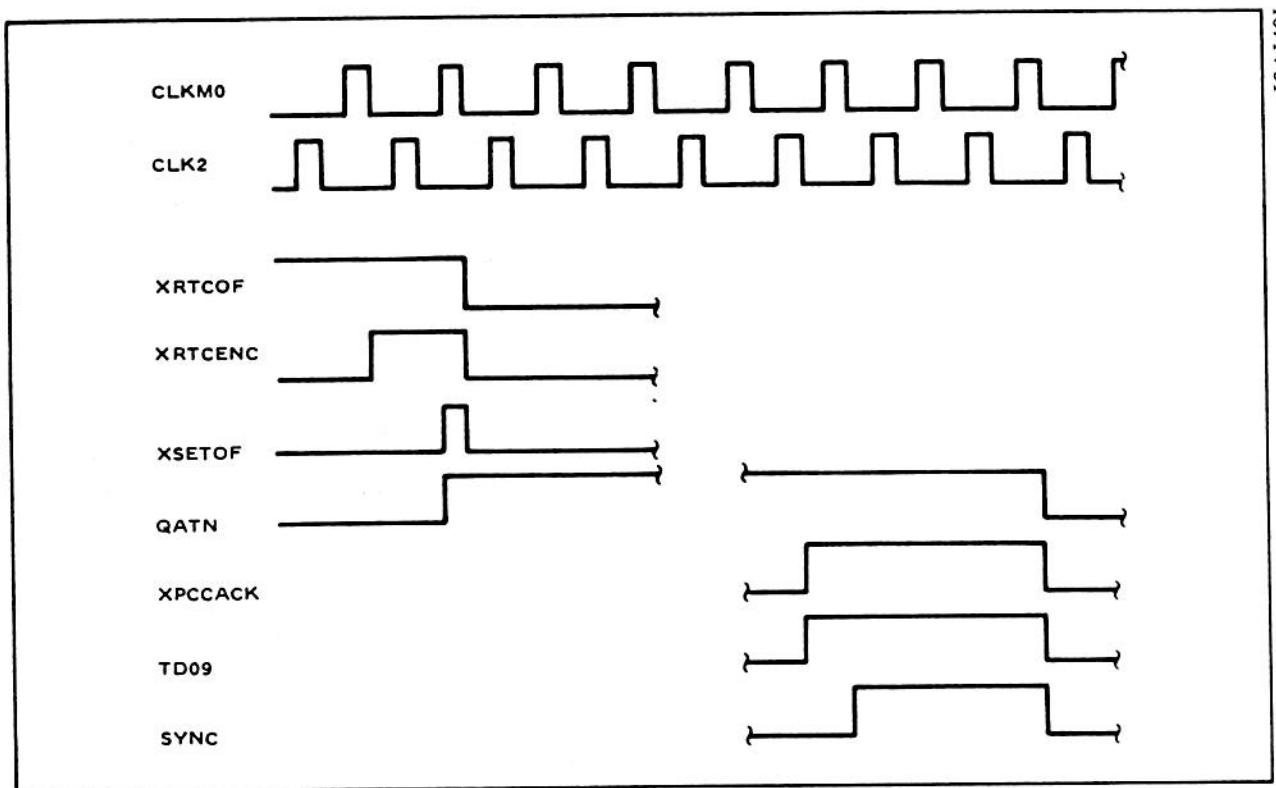

Figure 1-2 represents the HMP-1116 I/O Mux Bus interface. The interface is common to all I/O devices connected to the HMP-1116. All information (device address, commands, status and data) is transferred via the bidirectional data bus ( $\bar{T}D00-15$ ). The type of information is defined by the flag set by the computer.

The Address Flag ( $\bar{T}ADRS$ ) is set active when the 8 LSBs ( $\bar{T}D08-15$ ) contain a device address. The device whose address is on the data lines will respond by setting the Sync ( $\bar{T}SYN$ ) active. This informs the HMP-1116 microprogram that the device has received and decoded its address. This device will now be able to receive a command, send its status or transfer data.

The Command Flag ( $\bar{T}CMD$ ) is set active by the microprogram when the 9 LSBs of the I/O Mux Bus ( $\bar{T}D08-15$ ) contain a command for the addressed device. When the device receives this command it responds by setting  $\bar{T}SYN$  active.

When the Status Flag ( $\bar{T}SR$ ) is set active the addressed device will place its 8-bit status on the I/O Mux Bus LSBs and set  $\bar{T}SYN$  active.

The addressed I/O device sets the Halfword Flag ( $\bar{T}HW$ ) active if it can send or receive 16 bits of data at a time. If the device does not set  $\bar{T}HW$  active it can only send or receive 8 bits of data at a time. The microprogram examines  $\bar{T}HW$  prior to sending or receiving data.

The Data Available Flag ( $\bar{T}DA$ ) is set active when the I/O Mux Bus contains data for the addressed device. Data will be either 16 bits (on  $\bar{T}D00-15$ ) or 8 bits (on  $\bar{T}D08-15$ ) depending on the state of  $\bar{T}HW$ . The device responds with  $\bar{T}SYN$  when it receives the data.

When the Data Request Flag ( $\bar{T}DR$ ) is set active, the addressed device will place either 16 bits (on  $\bar{T}D00-15$ ) or 8 bits (on  $\bar{T}D08-15$ ) on the I/O Mux Bus (depending on the state of  $\bar{T}HW$ ) and set  $\bar{T}SYN$  active.

An interrupt from an I/O device is a request for service. The Interrupt Flag ( $\bar{T}ATN$ ) is common to all devices connected to the I/O Mux Bus. When  $\bar{T}ATN$  goes active, the computer must determine which device set the interrupt. To accomplish this the Acknowledge Flag ( $\bar{T}ACK$ ) is set active by the HMP-1116. The highest priority I/O device that has an interrupt pending will place its own device address on  $\bar{T}D08-15$  to identify itself as the interrupting device and sets  $\bar{T}SYN$  active.

Figure 1-1. HMP-1116 Processor Architecture

Figure 1-1A. HMP-1116 Memory Architecture

Figure 1-2. HMP-1116 I/O Mux Bus Interface

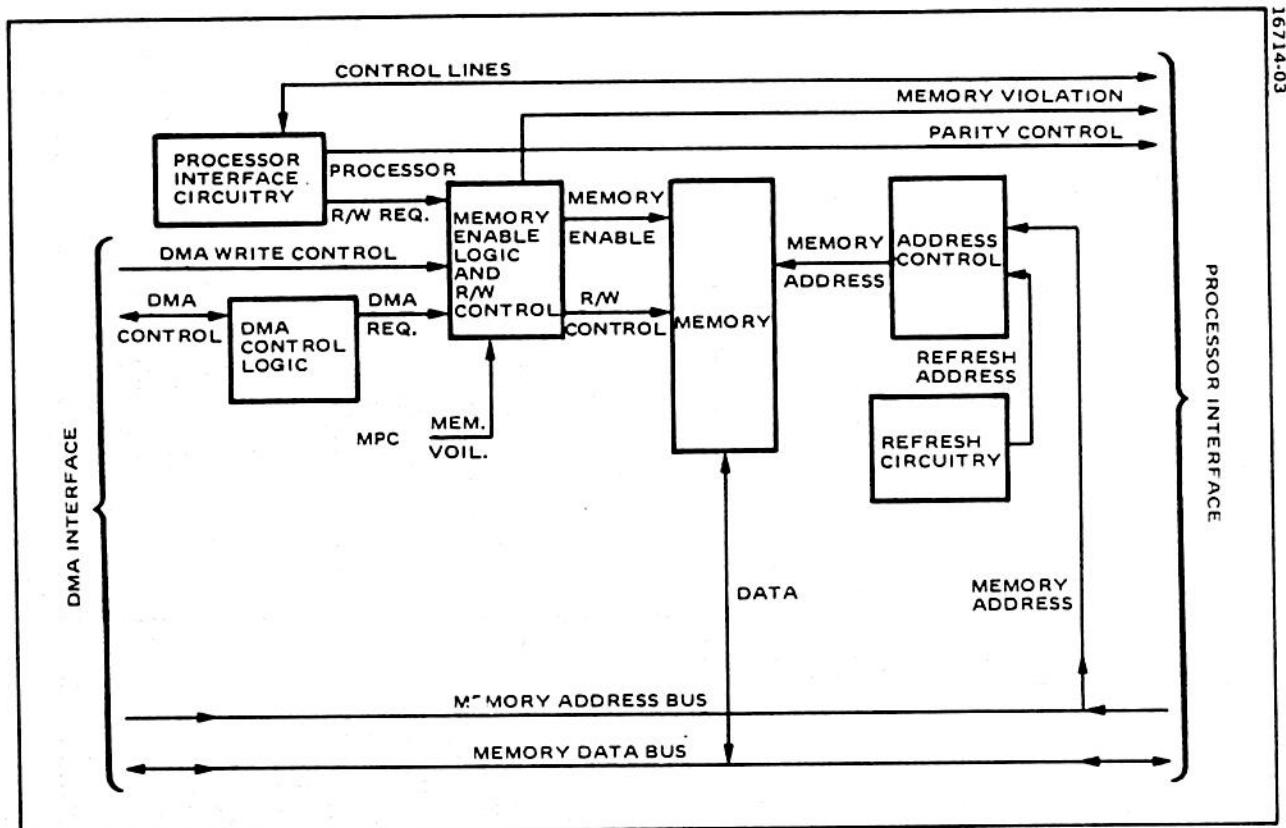

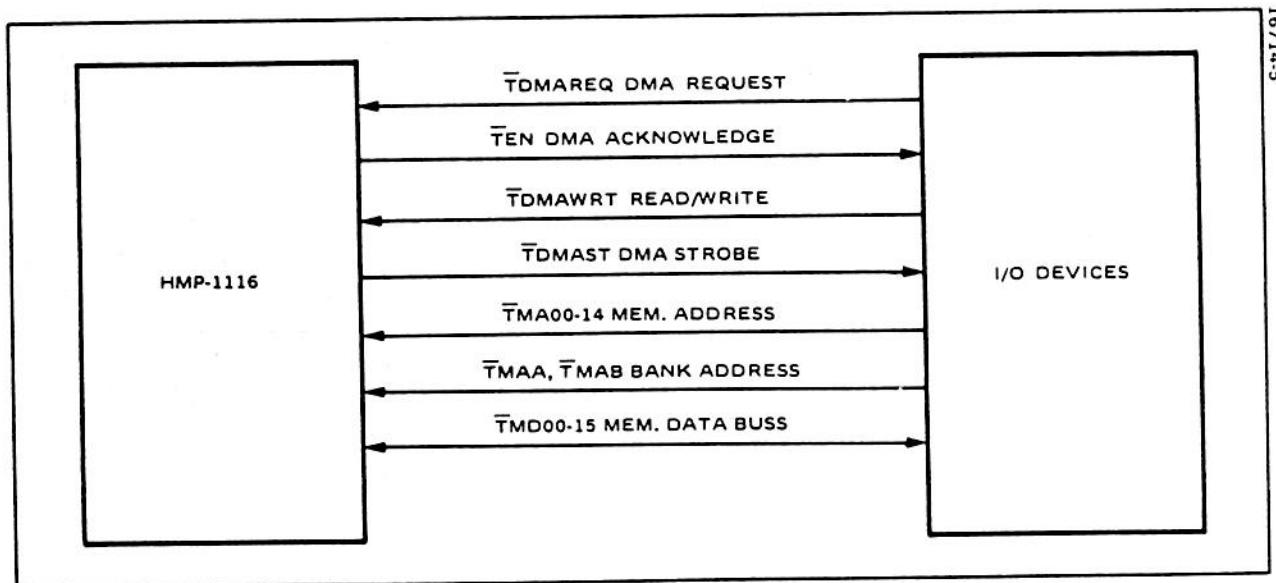

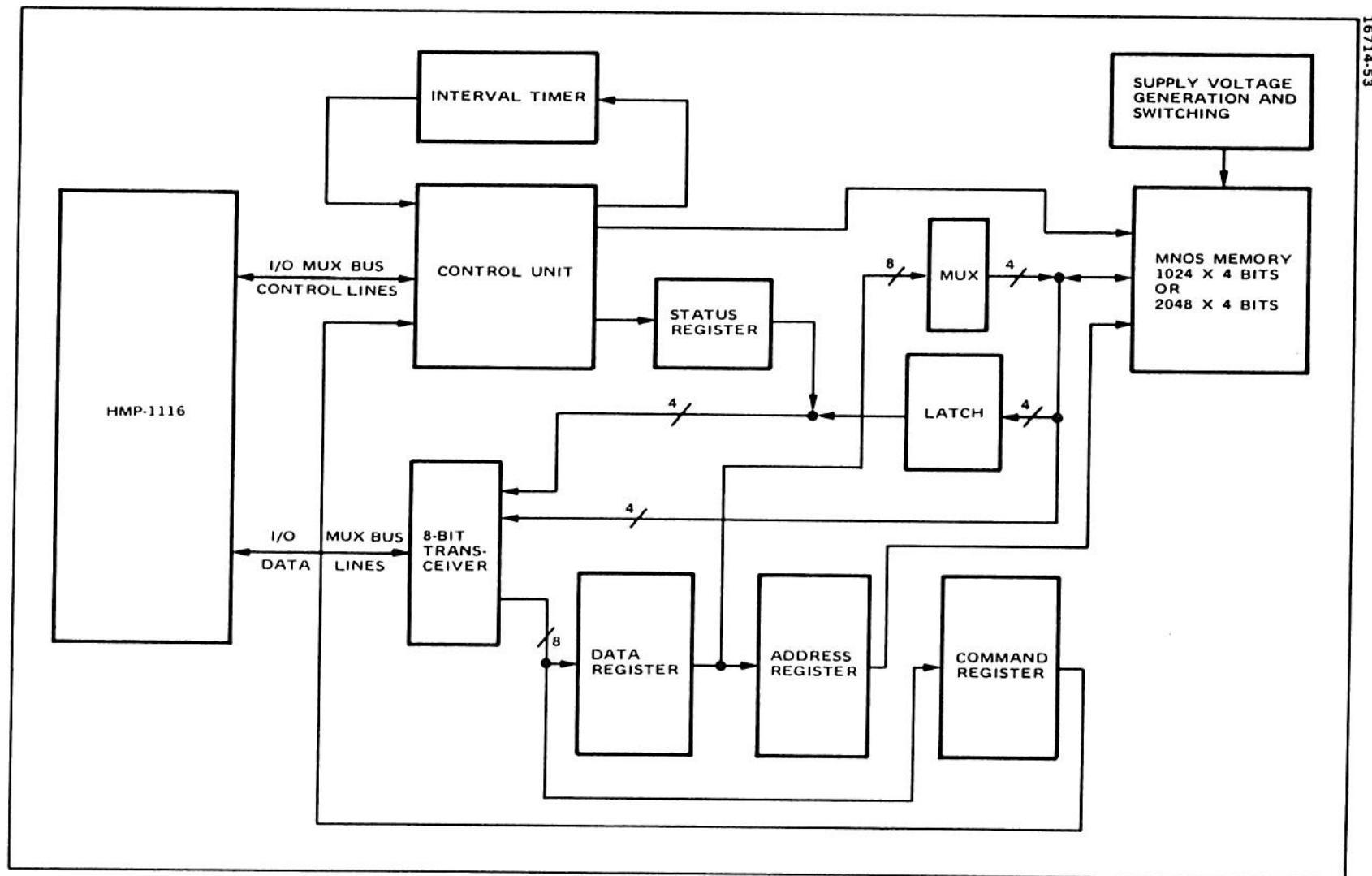

1.7 1.7 DMA Interface. The Direct Memory Access (DMA) Bus allows an external device to address HMP-1116 memory and read or write data. All DMA devices have an I/O Mux Bus interface also. The I/O interface provides initialization data (such as the starting address in the HMP-1116 memory) to be used by the DMA device during data transfers. The DMA device is responsible for updating the memory address and maintaining a word count when transferring a group of data.

Figure 1-3 represents the DMA Bus interface. The DMA Request (TDMAREQ) is set active by the DMA device when it wants to use memory. The HMP-1116 responds with DMA Acknowledge (TEN).

#### DMA Read

When  $\bar{TEN}$  is received by the device it sends a 17-bit memory address ( $\bar{TMAA}$ ,  $\bar{TMAB}$ ,  $\bar{TMA00-14}$ ) to the HMP-1116. It also indicates that it wants to read from memory by setting the Read/Write Control ( $\bar{TDMAWRT}$ ) inactive. The DMA Strobe ( $\bar{TDMAST}$ ) will indicate that memory data is ready to be taken from the Memory Data Bus ( $\bar{TMD00-15}$ ). At this time the DMA device must accept the data and remove the memory address and Read/Write Control.

#### DMA Write

When  $\bar{TEN}$  is received by the DMA device it places memory address, Read/Write Control and memory data to be written into the HMP-1116 on the DMA Bus. The DMA Strobe will indicate that data has been written into memory. When the DMA Strobe is received, the device must remove memory address, Read/Write Control and data from the DMA Bus.

Figure 1-3. HMP-1116 DMA Bus Interface

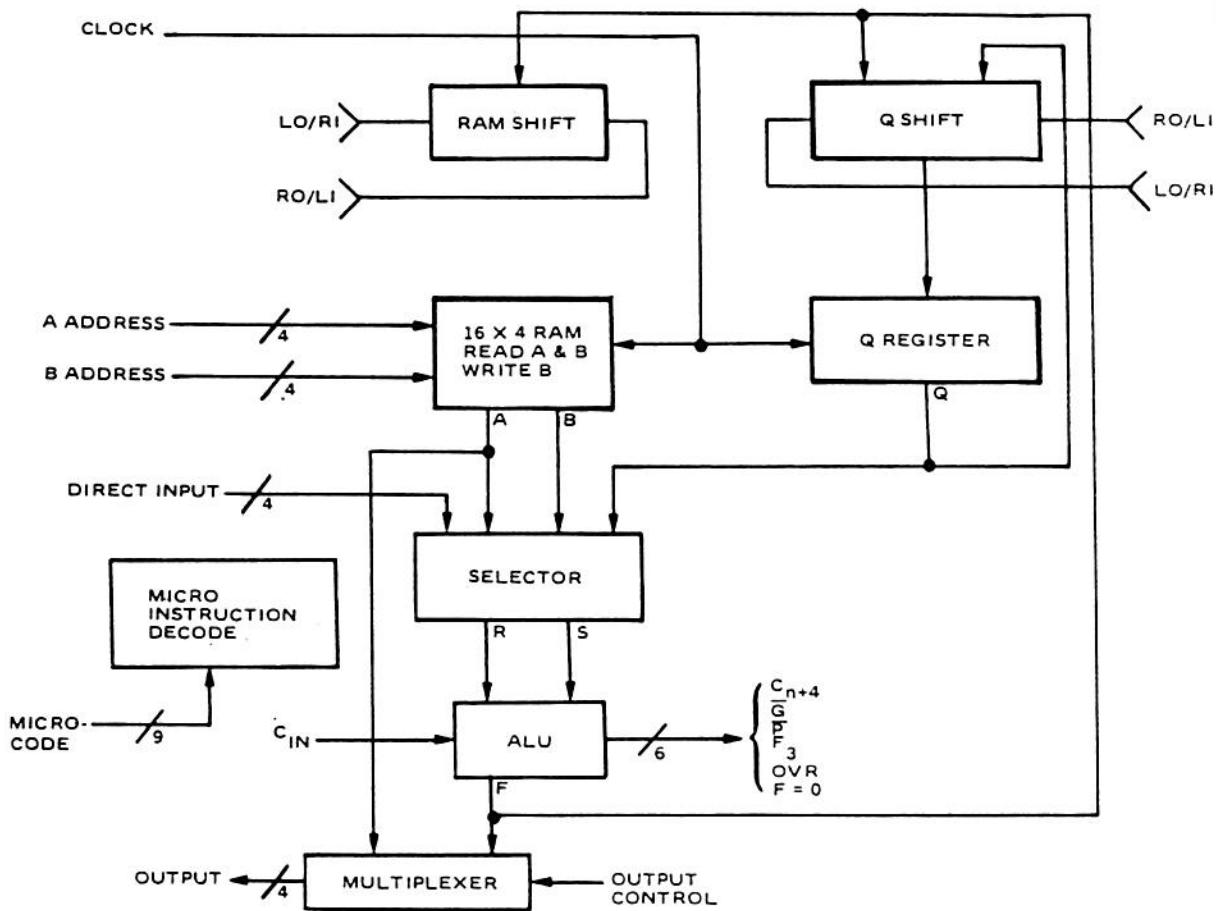

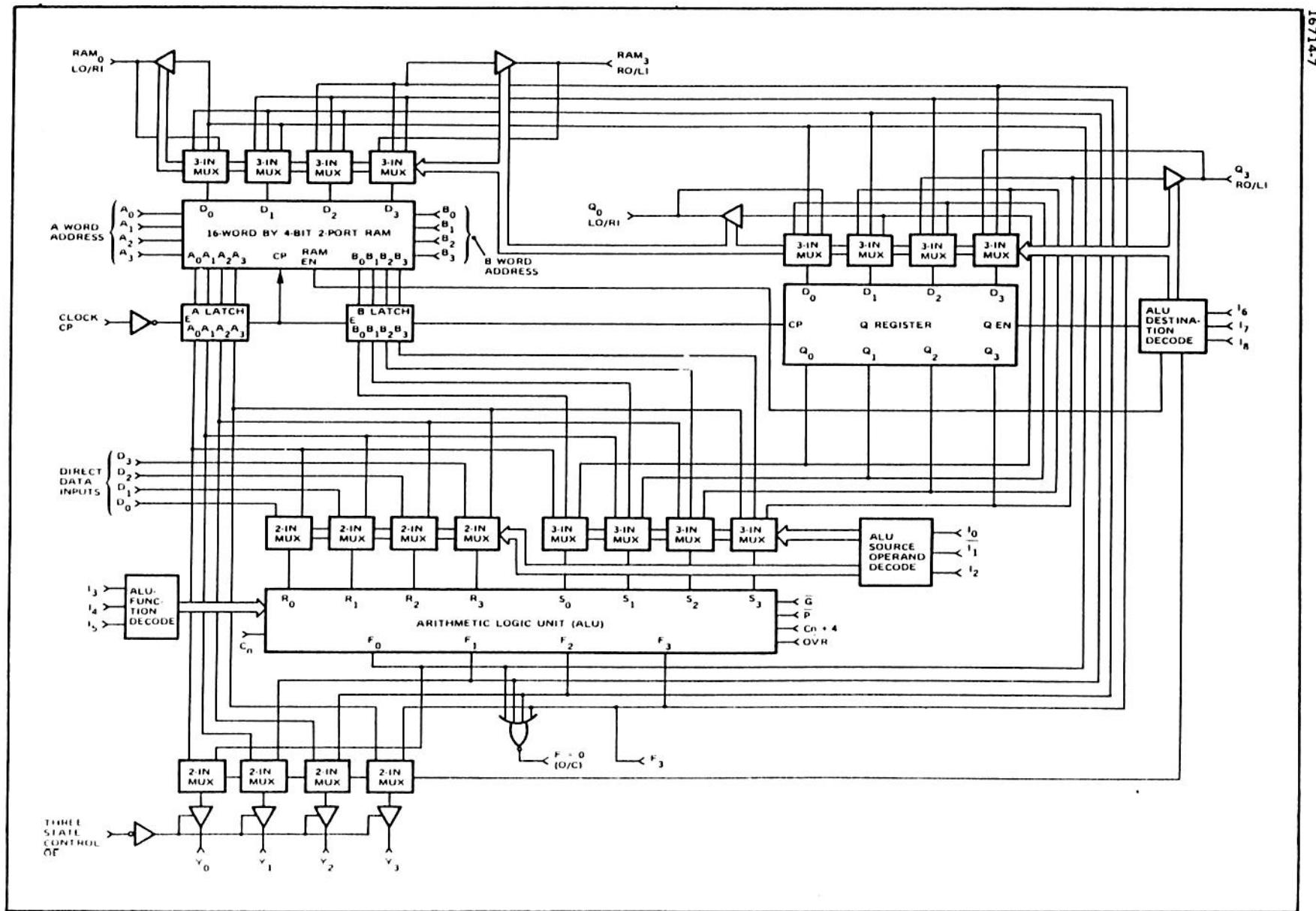

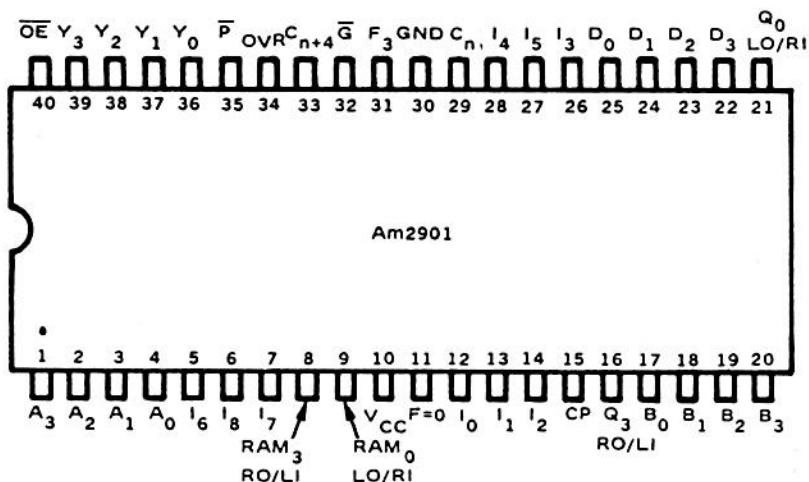

# Am2901

## Four-Bit Bipolar Microprocessor Slice

16714-9

| DISTINCTIVE CHARACTERISTICS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | GENERAL DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <ul style="list-style-type: none"> <li>• 16-word x 4-bit two-port RAM.</li> <li>• High speed ALU.</li> <li>• 9-bit microinstruction word.</li> <li>• Advanced low-power Schottky processing.</li> <li>• Four-bit slice cascadable to any number of bits with full carry look-ahead.</li> <li>• Three-state outputs.</li> <li>• Shift left, no shift, or shift right entry into RAM from ALU.</li> <li>• Output multiplexer for direct RAM A-port access or ALU output.</li> <li>• Status flags include carry-out, sign-bit (negative), overflow and zero detect.</li> <li>• Four-bit Q-register for scratch pad or accumulator extension.</li> <li>• Direct ALU entry to Q-register.</li> <li>• Shift Q-register left or right.</li> <li>• RAM-shift and Q-shift are easily cascadable.</li> </ul> | <p>The four-bit bipolar microprocessor slice is designed as a high-speed cascadable element intended for use in CPU's, peripheral controllers, programmable microprocessors and numerous other applications. The microinstruction flexibility of the Am2901 will allow efficient emulation of almost any digital computing machine.</p> <p>The device, as shown in the block diagram below consists of a 16-word by 4-bit two-port RAM, a high-speed ALU and the associated shifting, decoding and multiplexing circuitry. The nine-bit microinstruction word is organized into three groups of three bits each and selects the ALU source operands, the ALU function, and the ALU destination register. The microprocessor is cascadable with full look-ahead or with ripple carry, has three-state outputs, and provides various status flag outputs from the ALU. Advanced low-power Schottky processing is used to fabricate this 40-lead LSI chip.</p> |

MICROPROCESSOR SLICE BLOCK DIAGRAM

## ARCHITECTURE

A detailed block diagram of the bipolar microprogrammable microprocessor structure is shown in Figure 1. The circuit is a four-bit slice cascadable to any number of bits. Therefore, all data paths within the circuit are four bits wide. The two key elements in the Figure 1 block diagram are the 16-word by 4-bit 2-port RAM and the high-speed ALU.

Data in any of the 16 words of the Random Access Memory (RAM) can be read from the A-port of the RAM as controlled by the 4-bit A address field input. Likewise, data in any of the 16 words of the RAM as defined by the B address field input can be simultaneously read from the B-port of the RAM. The same code can be applied to the A select field and B select field in which case the identical file data will appear at both the RAM A-port and B-port outputs simultaneously.

When enabled by the RAM write enable (RAM EN), new data is always written into the file (word) defined by the B address field of the RAM. The RAM data input field is driven by a 3-input multiplexer. This configuration is used to shift the ALU output data (F) if desired. This three-input multiplexer scheme allows the data to be shifted up (right) one bit position, shifted down (left) one bit position, or not shifted in either direction.

The RAM A-port data outputs and RAM B-port data outputs drive separate 4-bit latches. These latches hold the RAM data while the clock input is LOW. This eliminates any possible race conditions that could occur while new data is being written into the RAM.

The high-speed Arithmetic Logic Unit (ALU) can perform three binary arithmetic and five logic operations on the two 4-bit input words R and S. The R input field is driven from a 2-input multiplexer, while the S input field is driven from a 3-input multiplexer. Both multiplexers also have an inhibit capability; that is, no data is passed. This is equivalent to a "zero" source operand.

Referring to Figure 1, the ALU R-input multiplexer has the RAM A-port and the direct data inputs (D) connected as inputs. Likewise, the ALU S-input multiplexer has the RAM A-port, the RAM B-port and the Q register connected as inputs.

This multiplexer scheme gives the capability of selecting various pairs of the A, B, D, Q and "0" inputs as source operands to the ALU. These five inputs, when taken two at a time, result in ten possible combinations of source operand pairs. These combinations include AB, AD, AQ, A0, BD, BQ, B0, DQ, D0 and Q0. It is apparent that AD, AQ and A0 are somewhat redundant with BD, BQ and B0 in that if the A address and B address are the same, the identical function results. Thus, there are only seven completely non-redundant source operand pairs for the ALU. The Am2901 microprocessor implements eight of these pairs. The microinstruction inputs used to select the ALU source operands are the I<sub>0</sub>, I<sub>1</sub>, and I<sub>2</sub> inputs. The definition of I<sub>0</sub>, I<sub>1</sub>, and I<sub>2</sub> for the eight source operand combinations are as shown in Figure 2. Also shown is the octal code for each selection.

The two source operands not fully described as yet are the D input and Q input. The D input is the four-bit wide direct data field input. This port is used to insert all data into the working registers inside the device. Likewise, this input can be used in the ALU to modify any of the internal data files. The Q register is a separate 4-bit file intended primarily for multiplication and division routines but it can also be used as an accumulator or holding register for some applications.

The ALU itself is a high-speed arithmetic/logic operator capable of performing three binary arithmetic and five logic functions. The I<sub>3</sub>, I<sub>4</sub>, and I<sub>5</sub> microinstruction inputs are used to select the

ALU function. The definition of these inputs is shown in Figure 3. The octal code is also shown for reference. The normal technique for cascading the ALU of several devices is in a look ahead carry mode. Carry generate, G, and carry propagate, P, are outputs of the device for use with a carry-look-ahead-generator such as the Am2902 ('182). A carry-out, C<sub>n+4</sub>, is also generated and is available as an output for use as the carry flag in a status register. Both carry-in (C<sub>n</sub>) and carry-out (C<sub>n+4</sub>) are active HIGH.

The ALU has three other status-oriented outputs. These are F<sub>3</sub>, F = 0, and overflow (OVR). The F<sub>3</sub> output is the most significant (sign) bit of the ALU and can be used to determine positive or negative results without enabling the three-state data outputs. F<sub>3</sub> is non-inverted with respect to the sign bit output Y<sub>3</sub>. The F = 0 output is used for zero detect. It is an open-collector output and can be wire OR'ed between microprocessor slices. F = 0 is HIGH when all F outputs are LOW. The overflow output (OVR) is used to flag arithmetic operations that exceed the available two's complement number range. The overflow output (OVR) is HIGH when overflow exists. That is, when C<sub>n+3</sub> and C<sub>n+4</sub> are not the same polarity.

The ALU data output is routed to several destinations. It can be a data output of the device and it can also be stored in the RAM or the Q register. Eight possible combinations of ALU destination functions are available as defined by the I<sub>6</sub>, I<sub>7</sub>, and I<sub>8</sub> microinstruction inputs. These combinations are shown in Figure 4.

The four-bit data output field (Y) features three-state outputs and can be directly bus organized. An output control (OE) is used to enable the three-state outputs. When OE is HIGH, the Y outputs are in the high-impedance state.

A two-input multiplexer is also used at the data output such that either the A-port of the RAM or the ALU outputs (F) are selected at the device Y outputs. This selection is controlled by the I<sub>6</sub>, I<sub>7</sub>, and I<sub>8</sub> microinstruction inputs. Refer to Figure 4 for the selected output for each microinstruction code combination.

As was discussed previously, the RAM inputs are driven from a three-input multiplexer. This allows the ALU outputs to be entered non-shifted, shifted up one position (X2) or shifted down one position (÷2). The shifter has two ports; one is labeled RAM<sub>0</sub>-LO/RI and the other is labeled RAM<sub>3</sub>-RO/LI. Both of these ports consist of a buffer-driver with a three-state output and an input to the multiplexer. Thus, in the shift up mode, the RO buffer is enabled and the RI multiplexer input is enabled. Likewise, in the shift down mode, the LO buffer and LI input are enabled. In the no-shift mode, both the LO and RO buffers are in the high-impedance state and the multiplexer inputs are not selected. This shifter is controlled from the I<sub>6</sub>, I<sub>7</sub>, and I<sub>8</sub> microinstruction inputs as defined in Figure 4.

Similarly, the Q register is driven from a 3-input multiplexer. In the no-shift mode, the multiplexer enters the ALU data into the Q register. In either the shift-up or shift-down mode, the multiplexer selects the Q register data appropriately shifted up or down. The Q shifter also has two ports; one is labeled Q<sub>0</sub>-LO/RI and the other is Q<sub>3</sub>-RO/LI. The operation of these two ports is similar to the RAM shifter and is also controlled from I<sub>6</sub>, I<sub>7</sub>, and I<sub>8</sub> as shown in Figure 4.

The clock input to the Am2901 controls the RAM, the Q register, and the A and B data latches. When enabled, data is clocked into the Q register on the LOW-to-HIGH transition of the clock. When the clock input is HIGH, the A and B latches are open and will pass whatever data is present at the RAM outputs. When the clock input is LOW, the latches are closed and will retain the last data entered. If the RAM-EN is enabled, new data will be written into the RAM file (word) defined by the B address field when the clock input is LOW.

Figure 1. Detailed Am2901 Microprocessor Block Diagram

| MICRO CODE |       |       | ALU SOURCE OPERANDS |          |

|------------|-------|-------|---------------------|----------|

| $I_2$      | $I_1$ | $I_0$ | OCTAL CODE          | R      S |

| L          | L     | L     | 0                   | A      Q |

| L          | L     | H     | 1                   | A      B |

| L          | H     | L     | 2                   | O      Q |

| L          | H     | H     | 3                   | O      B |

| H          | L     | L     | 4                   | O      A |

| H          | H     | H     | 5                   | D      A |

| H          | H     | L     | 6                   | D      Q |

| H          | H     | H     | 7                   | D      O |

Figure 2. ALU Source Operand Control

| MICRO CODE |       |       | ALU FUNCTION |                      | SYMBOL                  |

|------------|-------|-------|--------------|----------------------|-------------------------|

| $I_5$      | $I_4$ | $I_3$ | OCTAL CODE   | ALU FUNCTION         | SYMBOL                  |

| L          | L     | L     | 0            | R PLUS S             | $R + S$                 |

| L          | L     | H     | 1            | S MINUS R            | $S - R$                 |

| L          | H     | L     | 2            | R MINUS S            | $R - S$                 |

| L          | H     | H     | 3            | R OR S               | $R \vee S$              |

| H          | L     | L     | 4            | R AND S              | $R \wedge S$            |

| H          | L     | H     | 5            | $\overline{R}$ AND S | $\overline{R} \wedge S$ |

| H          | H     | L     | 6            | R EX-OR S            | $R \vee \overline{S}$   |

| H          | H     | H     | 7            | R EX-NOR S           | $R \wedge \overline{S}$ |

Figure 3. ALU Function Control

| MICRO CODE |       |       | RAM FUNCTION |             | Q-REG. FUNCTION   |             | Y OUTPUT            | RAM SHIFTER               |                           | Q SHIFTER               |                         |        |

|------------|-------|-------|--------------|-------------|-------------------|-------------|---------------------|---------------------------|---------------------------|-------------------------|-------------------------|--------|

| $I_8$      | $I_7$ | $I_6$ | OCTAL CODE   | SHIFT       | LOAD              | SHIFT       | LOAD                | RAM <sub>0</sub><br>LO/RI | RAM <sub>3</sub><br>LI/RO | Q <sub>0</sub><br>LO/RI | Q <sub>3</sub><br>LI/RO |        |

| L          | L     | L     | 0            | —           | —                 | NONE        | ALU ( $F_i$ )       | F                         | Z                         | Z                       | Z                       |        |

| L          | L     | H     | 1            | —           | —                 | —           | —                   | F                         | Z                         | Z                       | Z                       |        |

| L          | H     | L     | 2            | NONE        | ALU ( $F_i$ )     | —           | —                   | A                         | Z                         | Z                       | Z                       |        |

| L          | H     | H     | 3            | NONE        | ALU ( $F_i$ )     | —           | —                   | F                         | Z                         | Z                       | Z                       |        |

| H          | L     | L     | 4            | LEFT (DOWN) | ALU ( $F_{i+1}$ ) | LEFT (DOWN) | Q-REG ( $Q_{i+1}$ ) | F                         | $F_0$                     | $IN_3$                  | $Q_0$                   | $IN_3$ |

| H          | L     | H     | 5            | LEFT (DOWN) | ALU ( $F_{i+1}$ ) | —           | —                   | F                         | $F_0$                     | $IN_3$                  | $Q_0$                   | $IN_3$ |

| H          | H     | L     | 6            | RIGHT (UP)  | ALU ( $F_{i-1}$ ) | RIGHT (UP)  | Q-REG ( $Q_{i-1}$ ) | F                         | $IN_0$                    | $F_3$                   | $IN_0$                  | $Q_3$  |

| H          | H     | H     | 7            | RIGHT (UP)  | ALU ( $F_{i-1}$ ) | —           | —                   | F                         | $IN_0$                    | $F_3$                   | $IN_0$                  | $Q_3$  |

Z = HIGH-IMPEDANCE

Figure 4. ALU Destination Control

+ = PLUS; - = MINUS; V = OR; A = AND; V = EX-OR

| R, S                    | $I_2$ | L     | L A, Q | L A, B | L H O, Q | L H O, B | H L O, A | H L D, A | H H D, Q | H H D, O |

|-------------------------|-------|-------|--------|--------|----------|----------|----------|----------|----------|----------|

| $I_5$ $I_4$ $I_3$ $C_n$ | $I_1$ | $I_0$ | 0      | 1      | 2        | 3        | 4        | 5        | 6        | 7        |

| L L L L R PLUS S H      | A+Q   | A+B   | Q      | B      | A        | D+A      | D+Q      | D        |          |          |

|                         | A+Q+1 | A+Q+1 | Q+1    | B+1    | A+1      | D+A+1    | D+Q+1    | D+1      |          |          |

| L L H L S MINUS R H     | Q-A-1 | B-A-1 | Q-1    | B-1    | A-1      | A-D-1    | Q-D-1    | -D-1     |          |          |

|                         | Q-A   | B-A   | Q      | B      | A        | A-D      | Q-D      | -D       |          |          |

| L H L L R MINUSS H      | A-Q-1 | A-B-1 | -Q-1   | -B-1   | -A-1     | D-A-1    | D-Q-1    | D-1      |          |          |

|                         | A-Q   | A-B   | -Q     | -B     | -A       | D-A      | D-Q      | D        |          |          |

| L H H L R RORS H        | AVQ   | AVB   | Q      | B      | A        | DVA      | DVQ      | D        |          |          |

|                         |       |       |        |        |          |          |          |          |          |          |

| H L L L R AND S H       | AAQ   | AAB   | 0      | 0      | 0        | DAA      | DAQ      | 0        |          |          |

|                         |       |       |        |        |          |          |          |          |          |          |

| H L H L R AND S H       | ĀAQ   | ĀAB   | Q      | B      | A        | DĀA      | DĀQ      | 0        |          |          |

|                         |       |       |        |        |          |          |          |          |          |          |

| H H L L R EX-ORS H      | AVV   | AVB   | Q      | B      | A        | DVV      | DVQ      | D        |          |          |

|                         |       |       |        |        |          |          |          |          |          |          |

| H H H L R EX-NORS H     | ĀVV   | ĀVB   | ĀQ     | ĀB     | ĀA       | DĀVV     | DĀVQ     | ĀD       |          |          |

|                         |       |       |        |        |          |          |          |          |          |          |

Figure 5. Source Operand and ALU Function Matrix

## SOURCE OPERANDS AND ALU FUNCTIONS

As discussed earlier, there are eight source operand pairs available to the ALU as selected by the  $I_5$ ,  $I_4$ , and  $I_2$  instruction inputs. The ALU can perform eight functions; five logic and three arithmetic. The  $I_3$ ,  $I_4$ , and  $I_5$  instruction inputs control this function selection. The carry input,  $C_n$ , also affects the ALU results when in the arithmetic mode. The  $C_n$  input is inhibited in the logic mode. When  $I_5$  through  $I_2$  and  $C_n$  are viewed together, the matrix of Figure 5 results. This matrix fully defines the ALU/source operand function for each state.

| $I_5\ I_4\ I_3\ I_2\ I_1\ I_0$ | OCTAL<br>1543,1210 | GROUP  | FUNCTION                |

|--------------------------------|--------------------|--------|-------------------------|

| 1 0 0 0 0 0                    | 40                 | AND    | A $\wedge$ Q            |

| 0 0 1                          | 41                 |        | A $\wedge$ B            |

| 1 0 1                          | 45                 |        | D $\wedge$ A            |

| 1 1 0                          | 46                 |        | D $\wedge$ Q            |

| 0 1 1 0 0 0                    | 30                 | OR     | A $\vee$ Q              |

| 0 0 1                          | 31                 |        | A $\vee$ B              |

| 1 0 1                          | 35                 |        | D $\vee$ A              |

| 1 1 0                          | 36                 |        | D $\vee$ Q              |

| 1 1 0 0 0 0                    | 60                 | EX-OR  | A $\vee$ Q              |

| 0 0 1                          | 61                 |        | A $\vee$ B              |

| 1 0 1                          | 65                 |        | D $\vee$ A              |

| 1 1 0                          | 66                 |        | D $\vee$ Q              |

| 1 1 1 0 0 0                    | 70                 | EX-NOR | $\overline{A \vee Q}$   |

| 0 0 1                          | 71                 |        | $\overline{A \vee B}$   |

| 1 0 1                          | 75                 |        | $\overline{D \vee A}$   |

| 1 1 0                          | 76                 |        | $\overline{D \vee Q}$   |

| 1 1 1 0 1 0                    | 72                 | INVERT | $\overline{Q}$          |

| 0 1 1                          | 73                 |        | $\overline{B}$          |

| 1 0 0                          | 74                 |        | $\overline{A}$          |

| 1 1 1                          | 77                 |        | $\overline{D}$          |

| 1 1 0 0 1 0                    | 62                 | PASS   | Q                       |

| 0 1 1                          | 63                 |        | B                       |

| 1 0 0                          | 64                 |        | A                       |

| 1 1 1                          | 67                 |        | D                       |

| 0 1 1 0 1 0                    | 32                 | PASS   | Q                       |

| 0 1 1                          | 33                 |        | B                       |

| 1 0 0                          | 34                 |        | A                       |

| 1 1 1                          | 37                 |        | D                       |

| 1 0 0 0 1 0                    | 42                 | "ZERO" | 0                       |

| 0 1 1                          | 43                 |        | 0                       |

| 1 0 0                          | 44                 |        | 0                       |

| 1 1 1                          | 47                 |        | 0                       |

| 1 0 1 0 0 0                    | 50                 | MASK   | $\overline{A} \wedge Q$ |

| 0 0 1                          | 51                 |        | $\overline{A} \wedge B$ |

| 1 0 1                          | 55                 |        | D $\wedge$ A            |

| 1 1 0                          | 56                 |        | D $\wedge$ Q            |

FIGURE 6. ALU LOGIC MODE FUNCTIONS

| $I_5\ I_4\ I_3\ I_2\ I_1\ I_0$ | OCTAL<br>1543,1210 | $C_n = 0$              |           | $C_n = 1$              |           |

|--------------------------------|--------------------|------------------------|-----------|------------------------|-----------|

|                                |                    | GROUP                  | FUNCTION  | GROUP                  | FUNCTION  |

| 0 0 0 0 0 0                    | 0 0                | ADD                    | A + Q     | ADD PLUS ONE           | A + Q + 1 |

| 0 0 1                          | 0 1                |                        | A + B     |                        | A + B + 1 |

| 1 0 1                          | 0 5                |                        | D + A     |                        | D + A + 1 |

| 1 1 0                          | 0 6                |                        | D + Q     |                        | D + Q + 1 |

| 0 0 0 0 1 0                    | 0 2                | PASS                   | Q         | INCREMENT              | Q + 1     |

| 0 1 1                          | 0 3                |                        | B         |                        | B + 1     |

| 1 0 0                          | 0 4                |                        | A         |                        | A + 1     |

| 1 1 1                          | 0 7                |                        | D         |                        | D + 1     |

| 0 0 1 0 1 0                    | 1 2                | DECRE                  | Q - 1     | PASS                   | Q         |

| 0 1 1                          | 1 3                |                        | B - 1     |                        | B         |

| 1 0 0                          | 1 4                |                        | A - 1     |                        | A         |

| 0 1 0 1 1 1                    | 2 7                |                        | D - 1     |                        | D         |

| 0 1 0 0 1 0                    | 2 2                | 1's COMP.              | -Q - 1    | 2's COMP.              | -Q        |

| 0 1 1                          | 2 3                |                        | -B - 1    |                        | -B        |

| 1 0 0                          | 2 4                |                        | -A - 1    |                        | -A        |

| 0 0 1 1 1 1                    | 1 7                |                        | -D - 1    |                        | -D        |

| 0 0 1 0 0 0                    | 1 0                | SUBTRACT<br>(1's COMP) | Q - A - 1 | SUBTRACT<br>(2's COMP) | Q - A     |

| 0 0 1                          | 1 1                |                        | B - A - 1 |                        | B - A     |

| 1 0 1                          | 1 5                |                        | A - D - 1 |                        | A - D     |

| 1 1 0                          | 1 6                |                        | Q - D - 1 |                        | Q - D     |

| 0 1 0 0 0 0                    | 2 0                |                        | A - Q - 1 |                        | A - Q     |

| 0 0 1                          | 2 1                |                        | A - B - 1 |                        | A - B     |

| 1 0 1                          | 2 5                |                        | D - A - 1 |                        | D - A     |

| 1 1 0                          | 2 6                |                        | D - Q - 1 |                        | D - Q     |

FIGURE 7. ALU ARITHMETIC MODE FUNCTIONS

16714-10

CONNECTION DIAGRAM

TOP VIEW

Am2901

NOTE: PIN 1 IS MARKED FOR ORIENTATION

FINAL DATA. THE PRELIMINARY DATA SHEET PRINTED 3-75 HAD PINS 5 AND 6 INTERCHANGED AND PINS 12 AND 14 INTERCHANGED WHEN COMPARED WITH THE ABOVE CONNECTION DIAGRAM.

ORDERING INFORMATION

| PACKAGE TYPE | TEMPERATURE RANGE | ORDER NUMBER |

|--------------|-------------------|--------------|

| HERMETIC DIP | 0°C TO +70°C      | AM2901DC     |

| DICE         | 0°C TO +70°C      | AM2901XC     |

| HERMETIC DIP | -55°C TO +125°C   | AM2901DM     |

| DICE         | -55°C TO +125°C   | AM2901XM     |

FURTHER INFORMATION

IF ADDITIONAL PRELIMINARY TECHNICAL INFORMATION IS REQUIRED, CONTACT THE NEAREST AMD SALES OFFICE OR CALL THE FACTORY IN SUNNYVALE, CALIFORNIA AND ASK FOR

JOHN SPRINGER

MARKETING MANAGER

BIPOLAR MICROPROCESSOR CIRCUITS

(408) 732-2400 OR TOLL FREE FROM OUTSIDE CALIFORNIA (800) 538-7904 OR 538-7989

16714.11

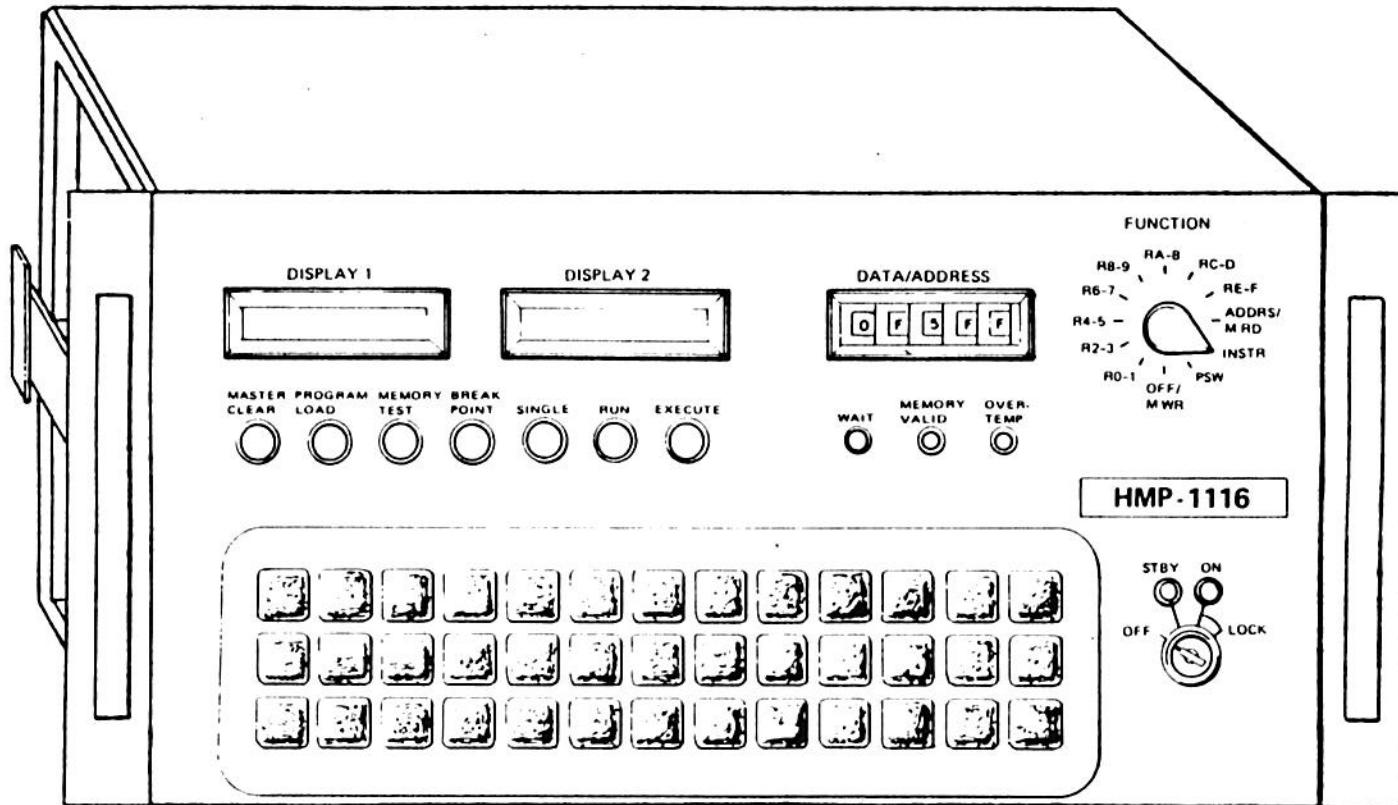

HMP-1116 Maintenance Panel

## HMP-1116 MAINTENANCE PANEL OPERATION

### A. TURN-ON PROCEDURE

1. Turn Key Switch to ON

2. All pushbuttons (MEMORY TEST, PROGRAM LOAD, BREAKPOINT, SINGLE and RUN) should be off (unlit)

3. Press MASTER CLEAR

### B. SPECIFYING A MEMORY ADDRESS

1. All pushbuttons off, FUNCTION SWITCH to ADRS/M RD

2. Enter desired address in the DATA/ADDRESS switches

3. Press EXECUTE; DISPLAY 1 = Program Status Register, DISPLAY 2 = Location Counter

### C. WRITING TO MEMORY

1. Select address to be written to by performing steps 1 thru 3 of "Specifying a Memory Address"

2. SINGLE on, FUNCTION SWITCH to OFF/M WR

3. Enter desired data in the DATA/ADDRESS switches

4. Press EXECUTE; DISPLAY 1 = Address + 2 written to, DISPLAY 2 = Data written

5. To write into sequential memory locations, repeat steps 3 and 4

### D. READING FROM MEMORY

1. Select address to be read from by performing steps 1 thru 3 of "Specifying a Memory Address"

2. SINGLE on

3. Press EXECUTE; DISPLAY 1 = Address + 2 read from, DISPLAY 2 = Data read

4. To read from sequential memory locations, repeat step 3

### E. READ GENERAL REGISTER OR PSW

1. All pushbuttons off

2. Select pair of Registers or PSW on FUNCTION SWITCH

3. Press EXECUTE; DISPLAY 1 = Even numbered Register or Program Status Reg.

DISPLAY 2 = Odd numbered Register or Location Counter

### F. READ FULLWORD (INSTRUCTION) FROM MEMORY

1. Select address to be read from by performing steps 1 thru 3 of "Specifying a Memory Address"

2. FUNCTION SWITCH to INSTR

3. Press EXECUTE; DISPLAY 1 = Contents of memory location specified by address

DISPLAY 2 = Contents of memory location specified by address+2

#### G. RUN A PROGRAM

1. Specify the start address of the program by performing steps 1 thru 3 of "Specifying a Memory Address"

2. RUN on, FUNCTION SWITCH to any position except ADRS/M RD or OFF/M WR

3. Press EXECUTE

#### H. RUN A PROGRAM IN SINGLE STEP

1. Perform steps 1 and 2 of "Run a Program"

2. SINGLE on

3. Press EXECUTE; DISPLAYS 1 and 2 will contain whatever the FUNCTION SWITCH specified (Register Pair, Updated PSW or next Instruction)

4. To execute successive instructions repeat step 3. The FUNCTION SWITCH can be changed between EXECUTE switch actions to select what will be displayed after the next instruction is executed.

#### I. RUN A PROGRAM IN BREAKPOINT

1. Perform steps 1 and 2 of "Run a Program"

2. BREAKPOINT on, enter instruction address in DATA/ADDRESS switches

3. Press EXECUTE; DISPLAY 1 = Specified breakpoint address

DISPLAY 2 MSD = 3 (if breakpoint was reached)

DISPLAY 2 LSDs = Instruction at breakpoint address

NOTE: Displays described in step 3 will only occur if the breakpoint address is reached; the MSD of DISPLAY 2 is the breakpoint indicator. Processor will stop before instruction at breakpoint address is executed.

#### J. PROGRAM LOAD USING THE 50-SEQUENCE LOADER

1. Perform operations required to prepare loader device (i.e. Put tape on Mag Tape Unit (MTU) and place MTU On-Line.)

2. PROGRAM LOAD on, all other pushbuttons off

3. Set DATA/ADDRESS switches to 'XXYY' where 'XX' is the loader device address, and 'YY' is command for device (i.e. '85A1' for MTU)

4. Press MASTER CLEAR

5. PROGRAM LOAD off, RUN on

6. Press EXECUTE; Program will load from specified loader device.

Remainder of procedure will be determined by the program loaded.

**K. PROGRAM LOAD OPTION USING DEVICE ADDRESS '00'**

1. Perform operations required to prepare loader device

2. PROGRAM LOAD and RUN on, all other pushbuttons off, FUNCTION SWITCH to PSW

3. Set DATA/ADDRESS switches to '000X' to specify loader device (see table below)

4. Press MASTER CLEAR; Program will load and run. Remainder of procedure will be determined by the program loaded.

| 'X' | DEVICE SPECIFIED    |

|-----|---------------------|

| 0   | Device Status Check |

| 1   | Mag Tape            |

| 2   |                     |

| 3   | Floppy Disc         |

| 4   | Disc Load           |

| 5   |                     |

| 6   |                     |

| 7   |                     |

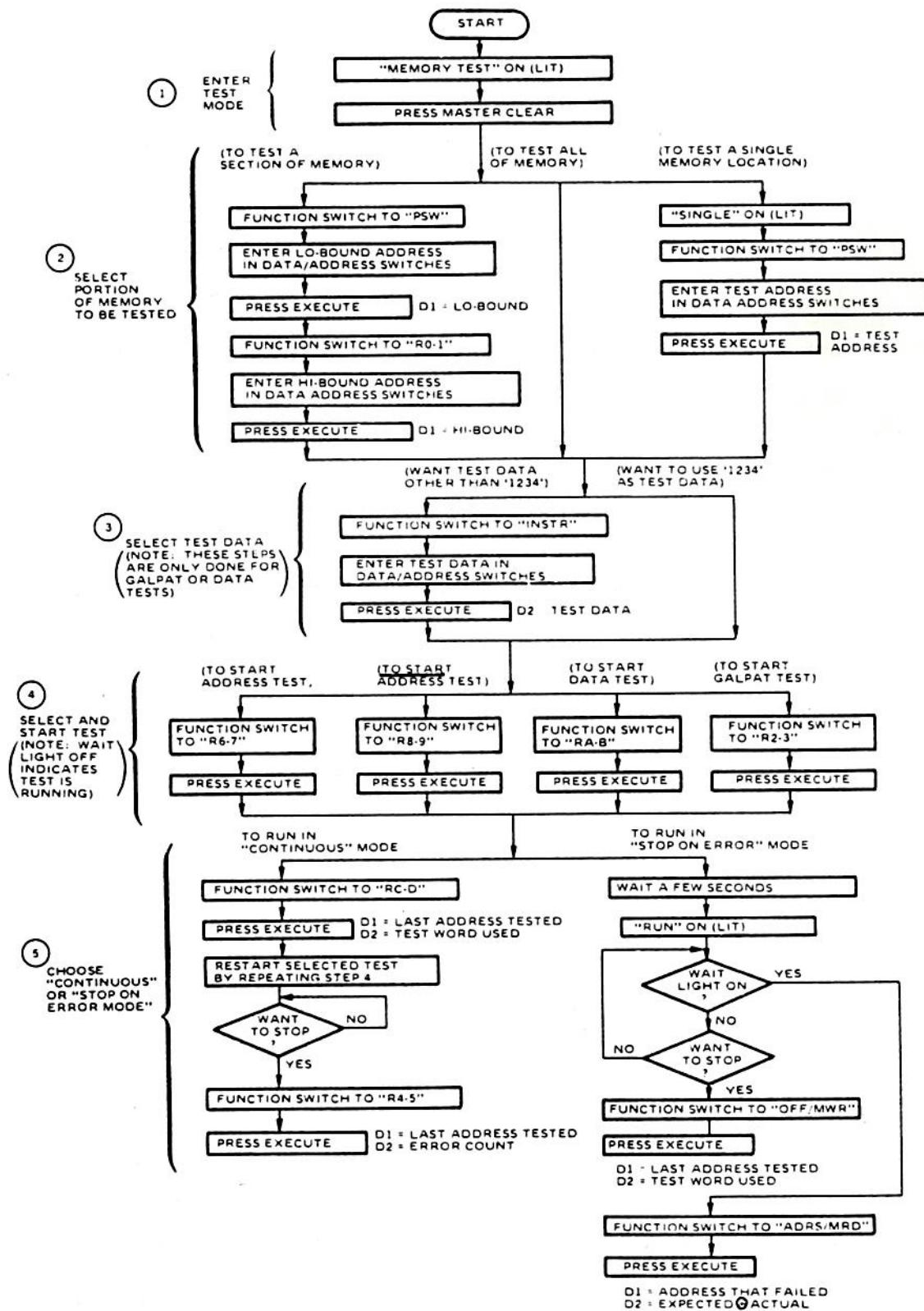

## MEMORY TEST

The Memory Test consists of four tests; 1) DATA, 2) GALPAT, 3) ADDRESS, and 4) ADDRESS.

The DATA test writes a fixed data pattern in all tested memory locations. The data pattern to be used is initially in DISPLAY 2.

The GALPAT test generates a pseudo-random data pattern from the value initially in DISPLAY 2. This test writes to a memory location and then changes adjacent locations in memory to see if the tested location is affected.

The ADDRESS test writes the address of a location into that location. For example, load location '0123' with '0123'.

The ADDRESS test writes the one's complement of the address of a location into that location. For example, load location '0123' with 'FEDC'.

Executing the memory test is broken into five steps; 1) enter the test mode, 2) select portion of memory to be tested, 3) select test data (for DATA and GALPAT tests only), 4) select and start test (either DATA, GALPAT, ADDRESS or ADDRESS) and 5) run test in either the "Continuous" or the "Stop on Error" mode.

When you enter the test mode, DISPLAY 1 will indicate the size of memory as shown in the table below:

| CONTENTS OF DISPLAY 1 | NUMBER OF MEMORY CARDS | SIZE OF MEMORY (1K = 1,024 Halfwords) |

|-----------------------|------------------------|---------------------------------------|

| 10000                 | 1                      | 32K                                   |

| 20000                 | 2                      | 64K                                   |

| 30000                 | 3                      | 96K                                   |

| 00000                 | 4                      | 128K                                  |

The "Continuous" mode continually tests the selected memory locations and maintains an error count.

The "Stop on Error" mode tests the selected memory locations until the first error occurs and then halts.

The memory test performs the following operation on each location tested, "read-check-write". Therefore, on the first pass through memory using new test data every "read-check-write" will result in an error being detected. This is why you wait a few seconds when running the "Stop on Error" mode, you are allowing time enough for the new test pattern to fill memory before allowing a stop on error to occur. This is also why you stop and restart in the "Continuous" mode, this is to clear out the error count after the new data has filled memory.

## HMP-1116 Memory Test

## 2.0 PROGRAMMING IN MACHINE LANGUAGE

2.1 Introduction. A program is a set of software instructions. These software instructions are arranged in a logical manner in order to perform the data manipulations necessary to solve a problem. The software instructions are loaded into consecutive memory locations. The Program Status Word (PSW) controls which instruction will be executed next and contains the status of the program. The format of the PSW is:

| 0    | 1      | 7            | 8            | 9              | 10               | 11 | 12 | 15 | 16 | 31 |

|------|--------|--------------|--------------|----------------|------------------|----|----|----|----|----|

| Wait | Status | Program Bank | Operand Bank | Condition Code | Location Counter |    |    |    |    |    |

When the PSW is loaded the Wait bit (PSW bit 0) will determine if the software program will be executed. Wait = 1 means halt. Wait = 0 means execute the software program.

The Status bits (PSW bits 1 through 7) control interrupts.

The Condition Code consists of four flags; the Carry flag (PSW bit 12), the Overflow flag (PSW bit 13), the Greater Than Zero flag (PSW bit 14) and the Less Than Zero flag (PSW bit 15). The four flags are normally abbreviated as C, V, G and L, respectively. The Condition Code is set by a previously executed software instruction.

The computer has an 18-bit memory address. Since the basic word length in the computer is 16 bits, special control is provided for the two MSBs of the memory address. These two bits are specified by either bits 8 and 9, or bits 10 and 11 of the PSW. They are called the memory bank address.

The next instruction to be executed is located in the bank specified by the Program Bank address (PSW bits 8 and 9), and the location within that bank is specified by the Location Counter (PSW bits 16 through 31). If a software instruction is using a memory location as an operand, the bank that operand is located in is specified by the Operand Bank address (PSW bits 10 and 11).

Memory is organized in 16-bit words. When the processor accesses memory 16 bits of data are transferred. The processor can handle a word from memory as a 16-bit halfword or as two 8-bit bytes. To aid the programmer in handling data as bytes, the processor assigns two memory addresses to each memory location. The two addresses assigned to a location are an even/odd pair of numbers. For example, the first halfword in memory is assigned memory addresses '00000' and '00001'. Using either address will result in accessing the same 16 bits in memory. If the programmer is using the first halfword in memory as a 16-bit operand, he would refer to it as memory location '00000'. If the programmer is using the first halfword in memory as two 8-bit operands, he would refer to the 8 MSBs as '00000' and to the 8 LSBs as '00001'.

Figure 2-1. Program Status Word

**2.2 Software Instruction Formats.** A software instruction is either a 16-bit halfword or a 32-bit fullword. The instruction is divided into groups of bits called fields. There are four software instruction formats. The 8 MSBs of all instructions is called the op-code (OP). The OP field specifies the instruction format and the operation to be performed. These halfword or fullword instructions are called the computer's machine language.

SHORT FORMAT (SF)

|    |     |   |    |    |    |

|----|-----|---|----|----|----|

| 0  | 7   | 8 | 11 | 12 | 15 |

| OP | R1* |   | N  |    |    |

The operands in an SF instruction are a General Register in File 1 specified by the R1 field and an immediate operand specified by the N field. A 16-bit immediate operand is created by setting the 3 MSDs (Most Significant Hex Digits) to zero and using N as the LSD (Least Significant Hex Digit). The General Register specified by R1 is the destination (where the result is placed).

REGISTER TO REGISTER (RR)

|    |     |   |    |    |    |

|----|-----|---|----|----|----|

| 0  | 7   | 8 | 11 | 12 | 15 |

| OP | R1* |   | R2 |    |    |

The operands in an RR instruction are two General Registers in File 1 specified by the R1 and R2 fields. The General Register specified by R1 is normally the destination.

REGISTER IMMEDIATE (RI)

|    |    |    |    |    |    |    |    |

|----|----|----|----|----|----|----|----|

| 0  | 7  | 8  | 11 | 12 | 15 | 16 | 31 |

| OP | R1 | X2 |    | I2 |    |    |    |

The operands in an RI instruction are a General Register in File 1 specified by the R1 field and an immediate operand dictated by the I2 and X2 fields. The 16-bit immediate operand is calculated by adding the 16-bit I2 field to the General Register specified by the X2 field. The register specified by the X2 field is called an index register. If the X2 field is zero, I2 alone is used as the immediate operand; in other words, no indexing will occur. The General Register specified by R1 is the destination.

REGISTER INDEXED MEMORY (RX)

|    |     |    |    |    |    |    |    |

|----|-----|----|----|----|----|----|----|

| 0  | 7   | 8  | 11 | 12 | 15 | 16 | 31 |

| OP | R1* | X2 |    | A2 |    |    |    |

The operands in an RX instruction are a General Register in File 1 specified by the R1 field and a memory location dictated by the A2 and X2 fields. The address of the memory location to be used is calculated by adding the 16-bit A2 field to the General Register (Index Register) specified by X2. If the X2 field is zero, no indexing will occur. Normally the General Register specified by R1 is the destination.

\* In some branch instructions R1 is replaced by the M1 field. The M1 field is compared bit for bit with the Condition Code to determine if the branch is to be taken. When an instruction branches, the instruction specifies the location of the next instruction to be executed.

2.3 Basic Instruction Set. For a complete description of the software instruction set, see Chapter 2 of the Technical Manual.

In the following examples the notation used to describe the operation performed is:

(Reg. X) is read "the contents of General Register X"

PSW(8:9) is read "PSW bits 8 through 9"

'1234' is a Hexadecimal quantity

['2000'] is read "the contents of memory location 2000"

← is read "is replaced with"

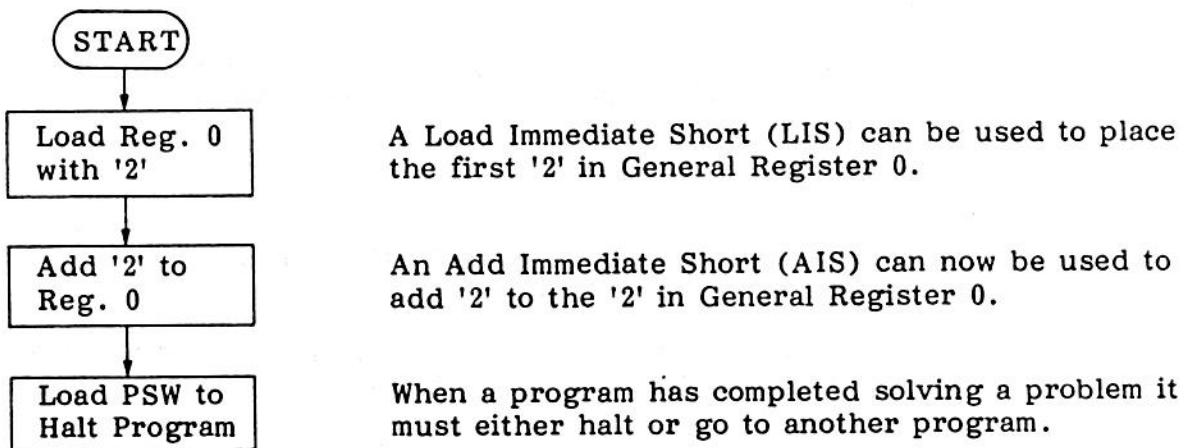

LOAD IMMEDIATE SHORT (LIS) 0 7 8 11 12 15

[24] R1 N (SF)

This instruction causes the General Register specified by R1 to be loaded with '000N'.

Example: [24 7 2] (Reg. 7) ← '0002'

Load General Register 7 with '0002'.

LOAD HALFWORD IMMEDIATE (LHI) 0 7 8 11 12 15 16 31

[C8] R1 X2 I2 (RI)

This instruction causes the General Register specified by R1 to be loaded with an immediate field specified by I2 plus the General Register specified by X2.

Example: [C8 2 0 0040] (Reg. 2) ← '0040'

Load General Register 2 with '0040'. This instruction has no indexing.

Example: [C8 5 1 12AB] (Reg. 5) ← '12AB' + (Reg. 1)

Load General Register 5 with the sum of '12AB' and the contents of General Register 1.

LOAD HALFWORD (LH) 0 7 8 11 12 15 16 31

[48] R1 X2 A2 (RX)

This instruction causes the General Register specified by R1 to be loaded from a memory location specified by A2 and X2. The bank in memory used is specified by PSW(10:11).

Example: [48 A 0 1000] (Reg. A) ← ['1000']

Load General Register A from memory location '1000'. No indexing.

Example: [48 0 A 2000] (Reg. 0) ← ['2000' + (Reg. A)]

Load General Register 0 from memory. The address of the memory location is calculated as '2000' plus the contents of General Register A.

STORE HALFWORD (STH)

| 0  | 7 | 8  | 11 | 12 | 15 | 16 | 31   |

|----|---|----|----|----|----|----|------|

| 40 |   | R1 | X2 |    | A2 |    | (RX) |

This instruction cause the General Register specified by R1 to be stored in a memory location specified by A2 and X2. The bank in memory used is specified by PSW(10:11).

Example:

|    |   |   |      |

|----|---|---|------|

| 40 | E | F | 02D0 |

|----|---|---|------|

['02D0' + (Reg. F)]  $\leftarrow$  (Reg. E)

Store General Register E in memory. The memory location is determined by adding the index register (General Register F) to '02D0'.

ADD IMMEDIATE SHORT (AIS)

| 0  | 7 | 8  | 11 | 12 | 15   |

|----|---|----|----|----|------|

| 26 |   | R1 | N  |    | (SF) |

This instruction causes the immediate operand '000N' to be added to the value currently in the General Register specified by R1.

Example:

|    |   |   |

|----|---|---|

| 26 | B | 5 |

|----|---|---|

(Reg. B)  $\leftarrow$  (Reg. B) + '0005'

Add '0005' to the contents of General Register B and store the result in General Register B.

SUBTRACT IMMEDIATE SHORT (SIS)

| 0  | 7 | 8  | 11 | 12 | 15   |

|----|---|----|----|----|------|

| 27 |   | R1 | N  |    | (SF) |

This instruction causes the immediate operand '000N' to be subtracted from the value currently in the General Register specified by R1.

Example:

|    |   |   |

|----|---|---|

| 27 | C | F |

|----|---|---|

(Reg. C)  $\leftarrow$  (Reg. C) - '000F'

Subtract '000F' from the contents of General Register C and store the result in General Register C.

LOAD PROGRAM STATUS WORD (LPSW)

| 0  | 7 | 8 | 11 | 12 | 15 | 16 | 31   |

|----|---|---|----|----|----|----|------|

| C2 |   | 0 | X2 |    | A2 |    | (RX) |

This instruction causes the PSW to be loaded from memory. The memory location is specified by the X2 and A2 fields. The R1 field is set to zero and has no effect on this instruction.

Example:

|    |   |   |      |

|----|---|---|------|

| C2 | 0 | 0 | F008 |

|----|---|---|------|

PSW(0:15)  $\leftarrow$  ['F008']

PSW(16:31)  $\leftarrow$  ['F00A']

Load the PSW from two consecutive memory locations. The first memory location is specified by 'F008' and it is loaded into the 16 MSBs of the PSW. The second memory location is 'F00A' and it is loaded into the 16 LSBs of the PSW.

#### COMPARE HALFWORD (CHR)

|    |   |    |    |    |      |

|----|---|----|----|----|------|

| 0  | 7 | 8  | 11 | 12 | 15   |

| 09 |   | R1 | R2 |    | (RR) |

This instruction algebraically compares the 16-bit operands in the General Registers specified by R1 and R2. The data in the two registers is unchanged as a result of this instruction. The G and L flags in the Condition Code indicate if the contents of the register specified by R1 are greater or less than the contents of the register specified by R2.

Example:

|    |   |   |

|----|---|---|

| 09 | 4 | 9 |

|----|---|---|

(Reg. 4) : (Reg. 9) (: means compared to)

This instruction causes the contents of General Register 4 to be compared to the contents of General Register 9. The contents are treated as two's complement operands. Both operands are unchanged. The G flag indicates that register 4 was greater than register 9. The L flag indicates that register 4 was less than register 9.

#### BRANCH ON FALSE BACKWARDS SHORT (BFBS)

|    |   |    |    |    |      |

|----|---|----|----|----|------|

| 0  | 7 | 8  | 11 | 12 | 15   |

| 22 |   | M1 | D  |    | (SF) |

The M1 field is compared bit for bit with the Condition Code. If none of the bits set in M1 match flags set in the Condition Code the condition is called false and a branch will be taken. When the branch is taken the branch address is calculated as the location of the BFBS instruction minus two times the D field. This is called relative addressing because the branch address is calculated relative to the location of the branch instruction.

Example:

|    |   |   |

|----|---|---|

| 22 | 2 | 4 |

|----|---|---|

If G flag not set, PSW(16:31)  $\leftarrow$  PSW(16:31) - '0008'

If G flag is set, PSW(16:31)  $\leftarrow$  PSW(16:31) + '0002'

(No branch)

The M1 (mask) in binary is 0010, and it is compared bit for bit with the flags CVGL in the Condition Code. If a flag set to 1 in the Condition Code corresponds to a 1 set in the mask, the condition is called true. Since only one bit is set in the mask field in this instruction only one flag will determine if the branch is to be taken, the G flag. If the G flag is not set, then the condition is false and the branch address is calculated as the Location Counter minus two times the D field ('4'). If the G flag is set, then the condition is true and the Location Counter is incremented by two to point at the next consecutive instruction. (Note: In all instructions the Location Counter is automatically incremented to point at the next consecutive instruction.)

### BRANCH ON TRUE FORWARDS SHORT (BTFS)

|    |   |    |    |    |      |

|----|---|----|----|----|------|

| 0  | 7 | 8  | 11 | 12 | 15   |

| 21 |   | M1 | D  |    | (SF) |

The M1 field is compared bit for bit with the Condition Code. If any of the bits set in M1 match flags set in the Condition Code the condition is called true and a branch will be taken. The relative branch address is calculated as the Location Counter plus two times the D field.

Example:

|    |   |   |

|----|---|---|

| 21 | 3 | F |

|----|---|---|

If G or L set, PSW(16:31)  $\leftarrow$  PSW(16:31) + '001E'

If G and L not set, PSW(16:31)  $\leftarrow$  PSW(16:31) + '0002'

(No branch)

Either the G or L flags being set will be a true condition and a relative branch will be calculated as the Location Counter plus '001E' (two times '00F').

| L | S | D | M | D | 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 9 | B | C | D | E | F |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| 0 |   |   |   |   | A | X |   | X | X | X | X | H | X | X | X |   |   |   |

| 1 | X |   |   |   |   | A | X |   | X | A | B |   | H | X | X | X | Y | X |

| 2 | X |   |   |   |   |   | A | X |   | X | A |   |   | X | P | Y | X | X |

| 3 | X |   |   |   |   |   |   | X | X | X | A |   | X | Q | D | X | X | Q |

| 4 | C |   |   |   |   |   |   |   | C | J | A | X | O | C | C | X | O |   |

| 5 | E | E | A |   |   |   |   |   | E | E | J | A | Y |   | E | Z |   |   |

| 6 | C |   | B |   |   |   |   |   | C | K | A | Z |   | C | Z | H |   |   |

| 7 | C |   | B |   |   |   |   |   | C | K | A | Z |   | C | Z | H |   |   |

| 8 | A | A | L | L | A | A | L | L | Z |   |   | A | Z | ! | X |   |   |   |

| 9 | F | F | M | M | F | F | M | M | Z |   |   | F | Z | ! | X |   |   |   |

| A | B | B | N | N | B | B | N | N | Z |   |   | B | Z | C | X |   |   |   |

| B | B | B | N | N | B | B | N | N | Z |   |   | B | Z | C | X |   |   |   |

| C | X | X | N | N | X | X | N | N | X |   |   | H | X | H |   |   |   |   |

| D | X | X | N | N | X | X | N | N | Z |   |   | H | Z | H |   |   |   |   |

| E | B |   | X |   | B |   |   |   |   | Z |   | I | Z | I |   |   |   |   |

| F | B |   | X |   | B |   |   |   |   | Z |   | I | Z | I |   |   |   |   |

TO FIND WHAT EFFECT AN INSTRUCTION HAS ON THE CONDITION CODE, USE THE TWO HEX DIGITS OF THE OP CODE TO FIND THE APPROPRIATE ENTRY IN THE MAP. THE LETTER FOUND IN THE MAP CORRESPONDS TO ONE OF THE DESCRIPTIONS BELOW.

A.

|   |   |   |   |

|---|---|---|---|

| C | V | G | L |

| X | X | 0 | 0 |

| X | X | 0 | 1 |

| X | X | 1 | 0 |

OPERAND IS ZERO

OPERAND IS LESS THAN ZERO

OPERAND IS GREATER THAN ZERO

B.

|   |   |   |   |

|---|---|---|---|

| C | V | G | L |

| X | X | 0 | 0 |

| X | X | 0 | 1 |

| X | X | 1 | 0 |

| X | 1 | X | X |

| 1 | X | X | X |

RESULT IS ZERO

RESULT IS LESS THAN ZERO

RESULT IS GREATER THAN ZERO

ARITHMETIC OVERFLOW

CARRY / BARROW

C.

|   |   |   |   |

|---|---|---|---|

| C | V | G | L |

| X | X | 0 | 0 |

| X | X | 0 | 1 |

| X | X | 1 | 0 |

LOGICAL RESULT IS ZERO

|   |   |   |   |

|---|---|---|---|

| C | V | G | L |

| X | X | 0 | 0 |

| X | X | 0 | 1 |

| X | X | 1 | 0 |

LOGICAL RESULT IS NOT ZERO

D.

|   |   |   |   |

|---|---|---|---|

| C | V | G | L |

| X | X | 0 | 0 |

| X | X | 0 | 1 |

| X | X | 1 | 0 |

NONE OF THE BITS OF THE RESULT SET

BIT 0 OF THE RESULT SET

ONE OR MORE OF BITS 1 THRU 15 OF THE RESULT SET

E.

|   |   |   |   |

|---|---|---|---|

| C | V | G | 1 |

| X | X | 0 | 0 |

| X | X | 0 | 1 |

| X | X | 1 | 0 |

| 1 | X | X | X |

| 0 | X | X | X |

FIRST OPERAND EQUAL TO SECOND OPERAND

FIRST OPERAND NOT EQUAL TO SECOND OPERAND

FIRST OPERAND LESS THAN SECOND OPERAND

FIRST OPERAND EQUAL TO OR GREATER THAN SECOND OPERAND

F.

|   |   |   |   |

|---|---|---|---|

| C | V | G | L |

| X | X | 0 | 0 |

| X | X | 0 | 1 |

| X | X | 1 | 0 |

| 1 | X | X | X |

| 0 | X | X | X |

FIRST OPERAND EQUAL TO SECOND OPERAND

FIRST OPERAND LESS THAN SECOND OPERAND

FIRST OPERAND GREATER THAN SECOND OPERAND

G.

|   |   |   |   |

|---|---|---|---|

| C | V | G | L |

| 0 | X | 0 | 0 |

| 1 | X | 0 | 1 |

| 1 | X | 1 | 0 |

| 0 | X | 0 | 1 |

| 0 | X | 1 | 0 |

FIRST OPERAND EQUALS SECOND OPERAND

FIRST OPERAND LESS THAN SECOND OPERAND

FIRST OPERAND GREATER THAN SECOND OPERAND

H.

|   |   |   |   |

|---|---|---|---|

| C | V | G | L |

| 0 | 0 | 0 | 0 |

| 0 | 0 | 0 | 1 |

| 0 | 1 | 0 | 0 |

| 0 | 1 | 0 | 1 |

| 1 | 0 | 0 | 0 |

| 1 | 0 | 0 | 1 |

| 1 | 0 | 1 | 0 |

| 1 | 0 | 1 | 1 |

RESULT IS ZERO

RESULT IS NOT ZERO

RESULT IS NOT ZERO

LAST BIT THAT WAS SHIFTED OUT WAS A ZERO

LAST BIT THAT WAS SHIFTED OUT WAS A ONE

I.

|   |   |   |   |

|---|---|---|---|

| C | V | G | L |

| 0 | 0 | 0 | 0 |

| 0 | 0 | 0 | 1 |

| 0 | 1 | 0 | 0 |

| 0 | 1 | 0 | 1 |

| 1 | 0 | 0 | 0 |

| 1 | 0 | 0 | 1 |

| 1 | 0 | 1 | 0 |

| 1 | 0 | 1 | 1 |

RESULT IS ZERO

RESULT IS LESS THAN ZERO

RESULT IS GREATER THAN ZERO

LAST BIT THAT WAS SHIFTED OUT WAS A ZERO

LAST BIT THAT WAS SHIFTED OUT WAS A ONE

O. V-FLAG INDICATES  $Y = Z = 0$  OR  $Y \neq Z$

P. V-FLAG INDICATES RESULT  $> 7FFF FFFF$

Q. V-FLAG INDICATES  $DX \neq CY$

X. FLAGS UNCHANGED

Y. NEW FLAGS DETERMINED BY PSW LOADED

Z. I/O INSTRUCTION V FLAG NORMALLY INDICATES TIMEOUT (FALSE SYNC) 35  $\mu$ SEC

J.

|   |   |   |   |

|---|---|---|---|

| C | V | G | L |

| 0 | 1 | 0 | 0 |

| 0 | 0 | 0 | 0 |

LIST OVERFLOW

ELEMENT ADDED SUCCESSFULLY

K.

|   |   |   |   |

|---|---|---|---|

| C | V | G | L |

| 0 | 1 | 0 | 0 |

| 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 0 |

LIST WAS ALREADY EMPTY

LIST IS NOW EMPTY

LIST IS NOT YET EMPTY

L.

|   |   |   |   |

|---|---|---|---|

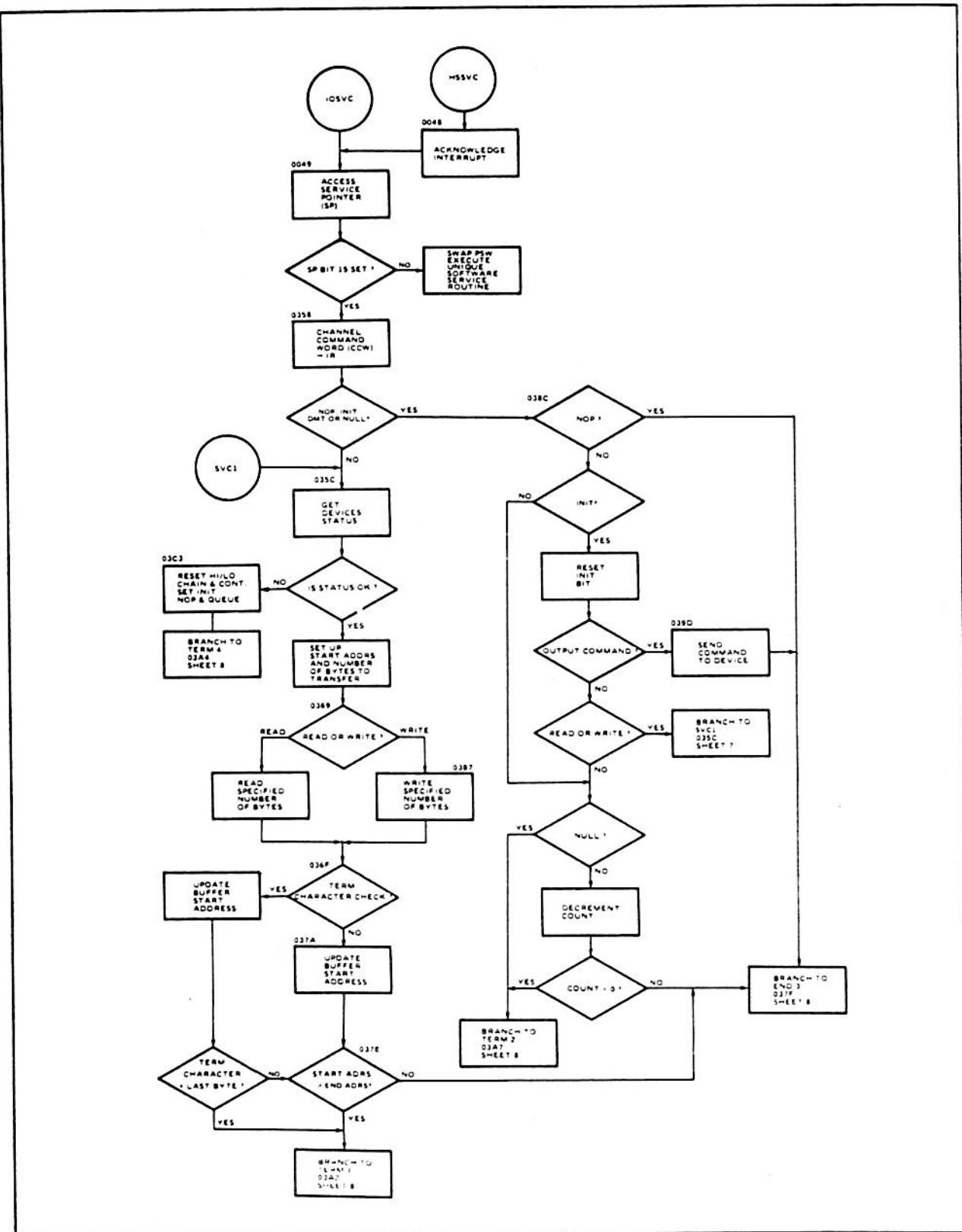

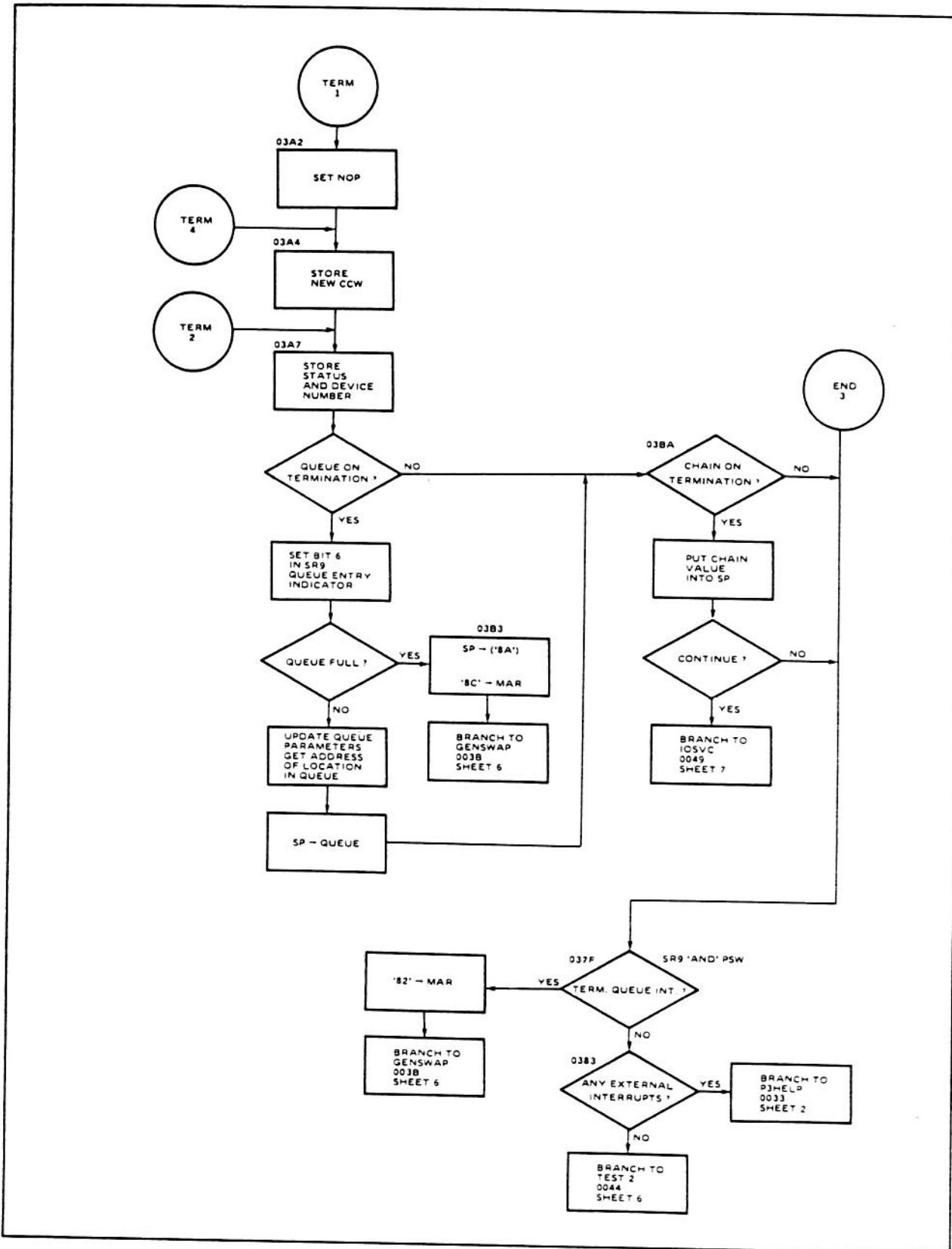

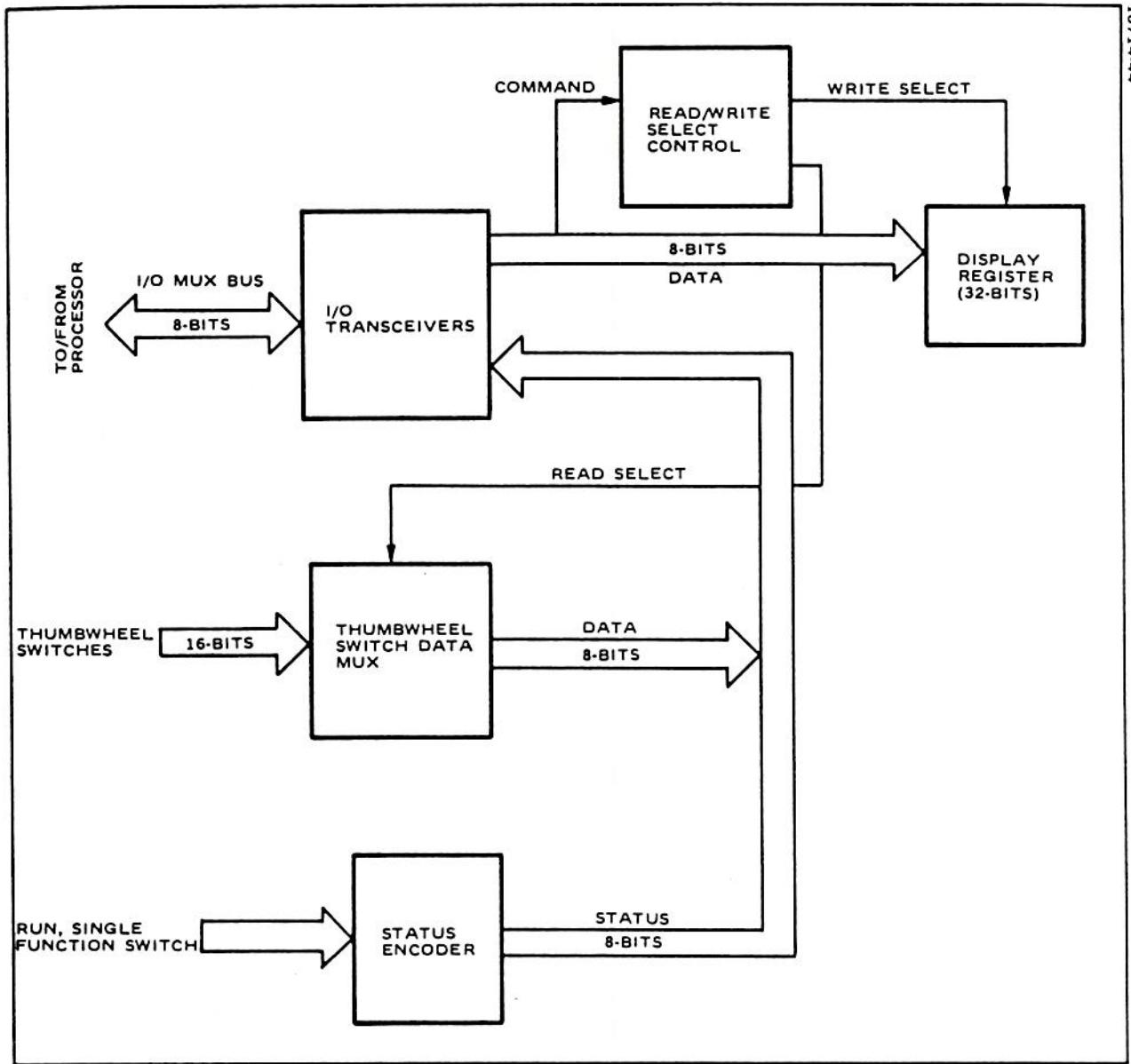

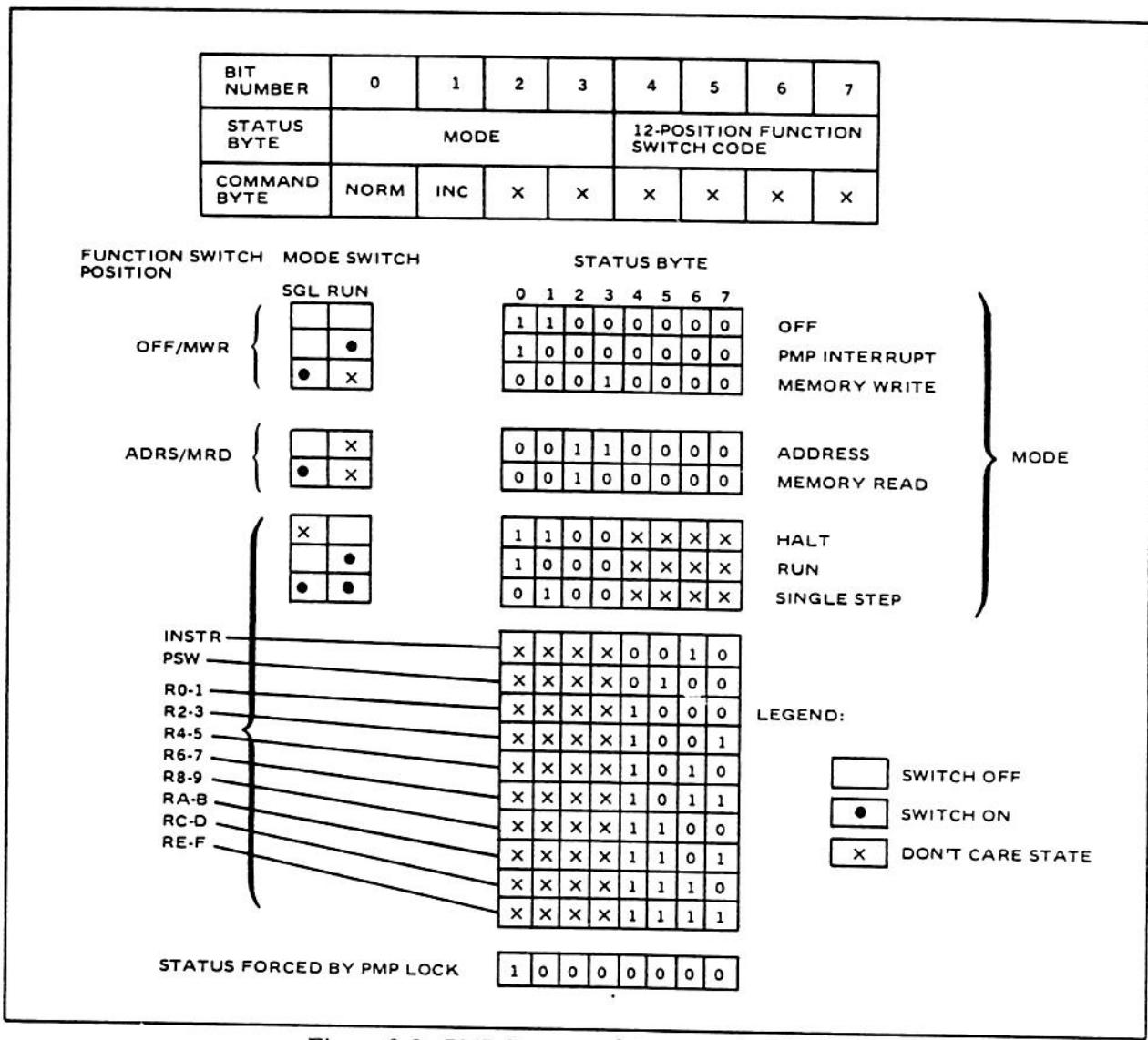

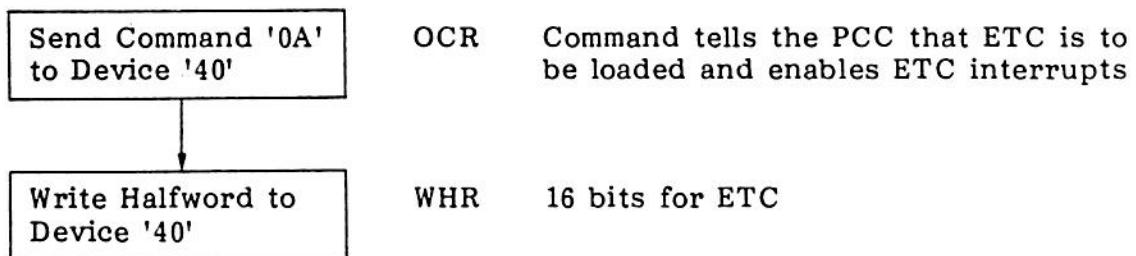

| C | V | G | L |